極向抽氣偏濾器,即把極向場外側的磁力線用專設線卷拉出來,使之與偏濾器板在設定位置、給定角度相交,從而控制雜質的產生與返流。

基本介紹

- 中文名:極向偏濾器

- 外文名:Poloidal divertor

- 套用學科:能源工程

- 範疇:工程技術

概述,極向偏濾器的套用,電路系統設計,實際電路參數測試結果,

概述

一般托卡馬克電漿是圓截面的。目前托卡馬克的特徵是採用D形截面帶有開放或封閉的、單或雙零點的偏濾器。當電漿截面拉長為D形時,它可以在更高的電漿電流下保持穩定。損失掉的電漿會轟擊器壁,造成雜質並發甚至過熱。極向抽氣偏濾器,即把極向場外側的磁力線用專設線卷拉出來,使之與偏濾器板在設定位置、給定角度相交,從而控制雜質的產生與返流。

極向偏濾器的套用

中國環流器二號A裝置(HL-2A)是我國第—個具有偏濾器位形的托卡馬克裝置,利用其極向偏濾器在高參數電漿條件下開展與偏濾器位形運行有關的研究。直觀的觀測核放射過程中核脈衝信號隨放射時間的強弱變化規律對於掌握受控核聚變有著重大的意義。我們為HL-2A裝置研製的多路分時積分器具有自動削掉輸入信號的負向反脈衝,積分時間0.2~1ms五檔可調,統一起始TTL觸發脈衝,20s自動定時工作,同時有十路信號積分的特點。

核聚變中,用氫的同位素氘和氚發生聚變,釋放巨大能量。其不產生溫室氣體和高放射性核廢料,氘和氚又可從海水中提取,是未來能源的希望所在。核工業西南物理研究院聚變科學所的中國環流器二號A裝置(HL-2A),是我國進行磁約束受控核聚變研究的第一個具有偏濾器位形的托卡馬克裝置。對聚變反應產生的射線進行分時積分,可研究核聚變反應隨時間變化的規律,我們設計的多路分時積分器的指標為:(1)對十路模擬脈衝信號(主放大器輸出)進行積分,並輸出時間幅度譜;(2)輸入的脈衝的負向反衝不能被積分;(3)積分時間選擇:0.2、0.4、0.6、0.8、1ms;(4)統一起始工作TTL觸發脈衝,一次總積分時間20s。

電路系統設計

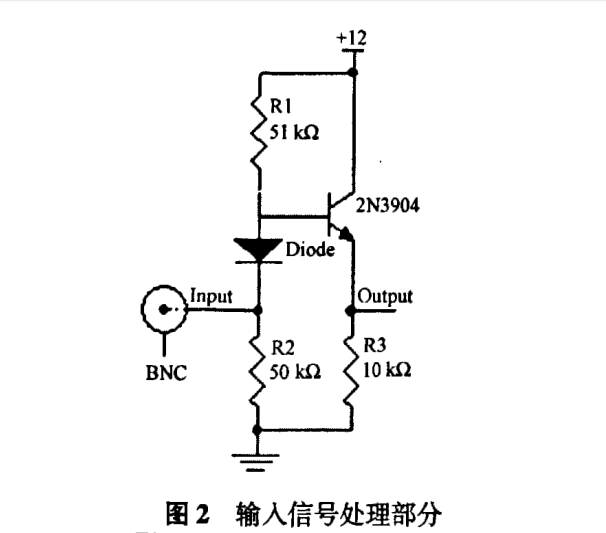

分時積分器工作原理如圖1。輸入信號先經過負向削波電路,把輸入信號的負向部分消除,然後經線性門到積分——保持電路進行脈衝積分,在外部系統給出觸發信號之後CPLD產生控制信號對積分一保持電路分別進行積分和保持並輸出結果。

圖1

圖1圖1多路分時積分電路可分為如下模組:(1)負向削波部分;(2)CPLD控制脈衝部分;(3)積分——保持部分;(4)系統觸發信號調節部分。

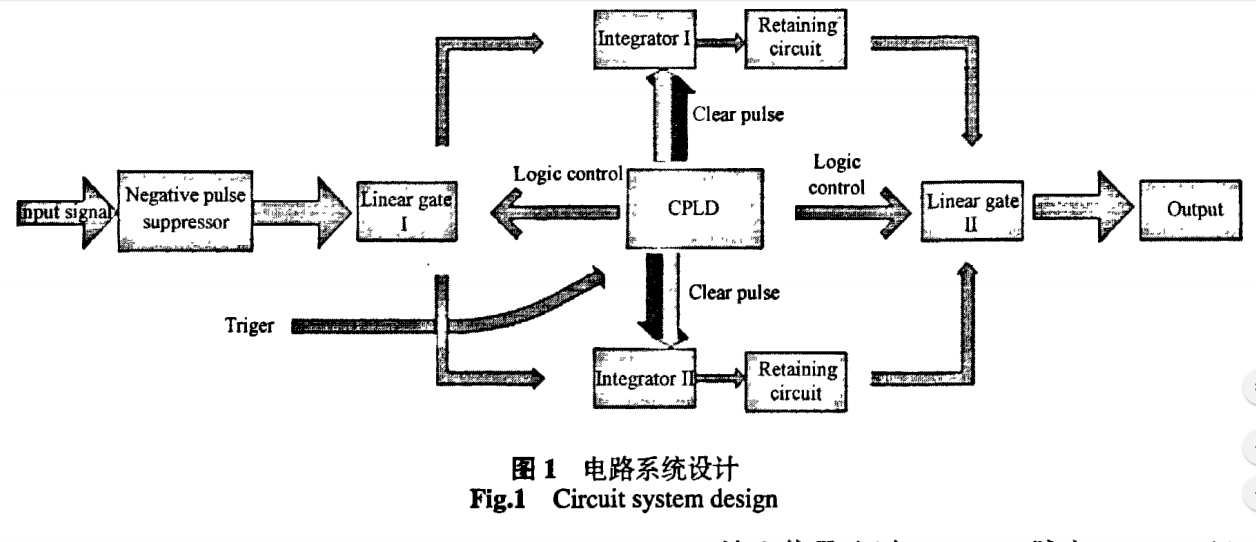

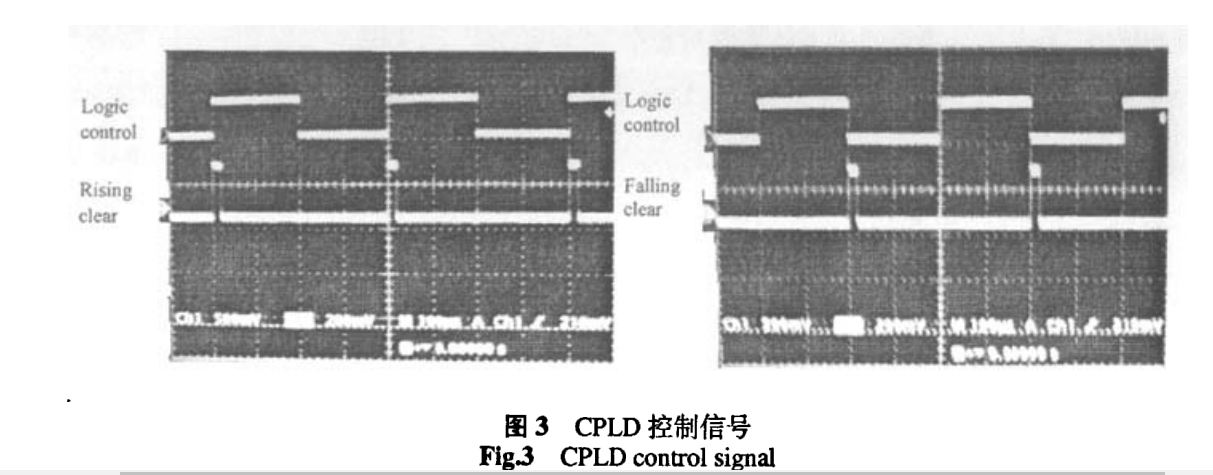

(1)負向削波部分:圖2是輸入信號處理電路,其主要的功能是把輸入信號中存在的負向過沖部分削去。

輸入信號(幅度 ,脈寬

,脈寬 )經二極體限制把負向信號削去,由三極體輸出。這裡,

)經二極體限制把負向信號削去,由三極體輸出。這裡, 以減少

以減少 電源帶來的直流電平影響。

電源帶來的直流電平影響。 以達到輸入匹配。調節

以達到輸入匹配。調節 阻值到

阻值到 ,可得到一個合適三極體工作的基極電流。

,可得到一個合適三極體工作的基極電流。

圖2

圖2經仿真與實測電路,該電路可以有效削除低至 的負向過沖信號對積分效果的影響。輸出信號部分經過電阻分壓和射隨器之後進入線性門。

的負向過沖信號對積分效果的影響。輸出信號部分經過電阻分壓和射隨器之後進入線性門。

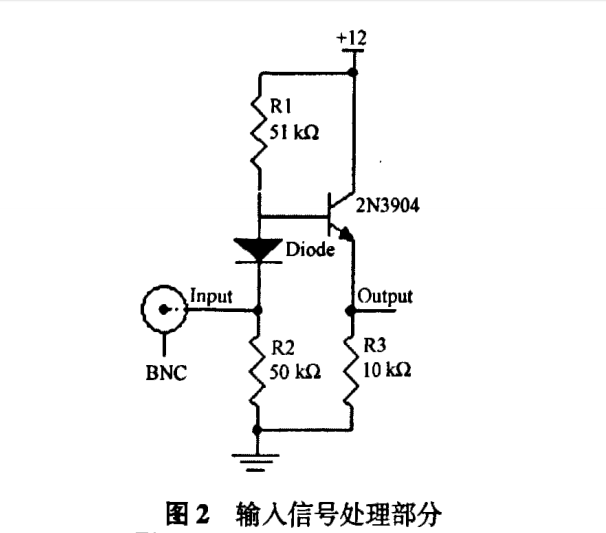

(2)CPLD控制脈衝部分:CPLD控制脈衝部分是在系統給出觸發信號後,開始工作20s。工作期間產生三個控制信號:(1)控制線性門開關的邏輯控制信號(0.2、0.4、0.6、0.8、1ms可調);(2)給積分器Ⅰ清零的上升沿清零脈衝(寬度20 );(3)給積分器Ⅱ清零的下降沿清零脈衝(寬度20

);(3)給積分器Ⅱ清零的下降沿清零脈衝(寬度20 )。

)。

CPLD時鐘產生主要步驟:(1)對TRIGER信號進行處理;(2)由(1)及8M晶振產生長度為20s工作時間;(3)由(2)及(1)計數產生工作時間內20 的信號;(4)由(3)工作時間內產生

的信號;(4)由(3)工作時間內產生 五檔時鐘信號;(5)5選1電路;(6)清零脈衝產生電路。

五檔時鐘信號;(5)5選1電路;(6)清零脈衝產生電路。

圖3

圖3圖3是實際電路在示波器上產生的控制脈衝信號波形。

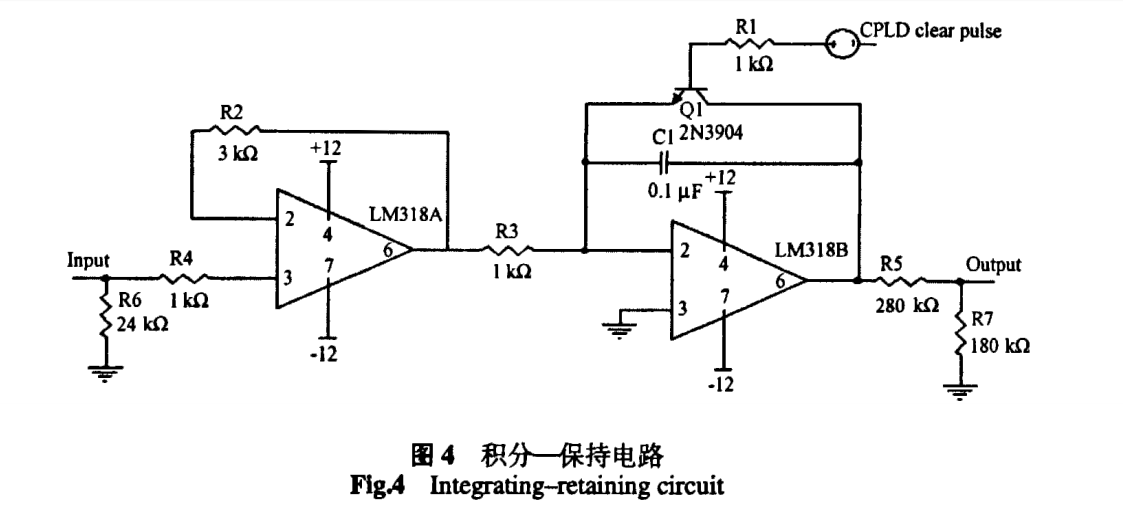

(3)積分——保持部分:圖4是積分——保持電路,其主要的功能是把從線性門過來的信號積分並分時輸出。

圖4

圖4線性門的信號先經過一個 的反向器後再積分輸出。若有觸發脈衝接入,CPLD產生邏輯控制信號和同步的清零脈衝信號。通過邏輯控制信號控制門選擇信號確定進入積分器Ⅰ或Ⅱ。信號輸入積分器後,先通過CPLD的清零脈衝在20

的反向器後再積分輸出。若有觸發脈衝接入,CPLD產生邏輯控制信號和同步的清零脈衝信號。通過邏輯控制信號控制門選擇信號確定進入積分器Ⅰ或Ⅱ。信號輸入積分器後,先通過CPLD的清零脈衝在20 內對上一個周期已積分信號清零,再對輸入信號積分。同時,另外一路積分器則對已積分信號保持輸出,即輸出—個信號幅度。邏輯控制信號到來後,積分的一路無輸人信號,停止積分,把最後積分到的幅度保持輸出;同時,另外一路清零後開始積分。我們採用桌球結構的積分器,即積分器Ⅰ積分時積分器Ⅱ作輸出,這給後續電路系統足夠的時間來處理積分器輸出的信號。

內對上一個周期已積分信號清零,再對輸入信號積分。同時,另外一路積分器則對已積分信號保持輸出,即輸出—個信號幅度。邏輯控制信號到來後,積分的一路無輸人信號,停止積分,把最後積分到的幅度保持輸出;同時,另外一路清零後開始積分。我們採用桌球結構的積分器,即積分器Ⅰ積分時積分器Ⅱ作輸出,這給後續電路系統足夠的時間來處理積分器輸出的信號。

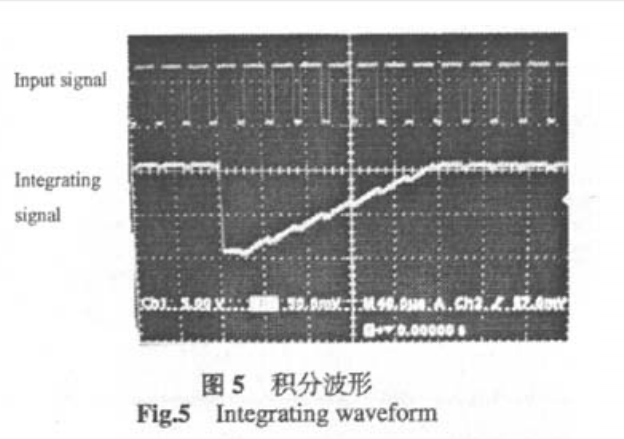

圖5

圖5圖5為在輸入方波信號後示波器顯示的積分信號(積分時間200 )。

)。

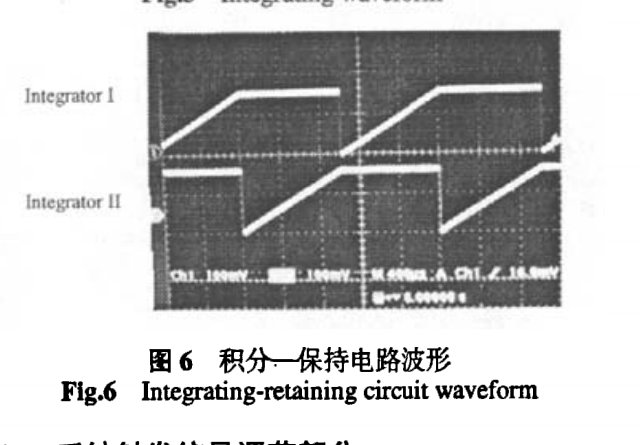

圖6

圖6圖6為示波器上同時觀察2路積分器的積分信號(積分時間1ms)。

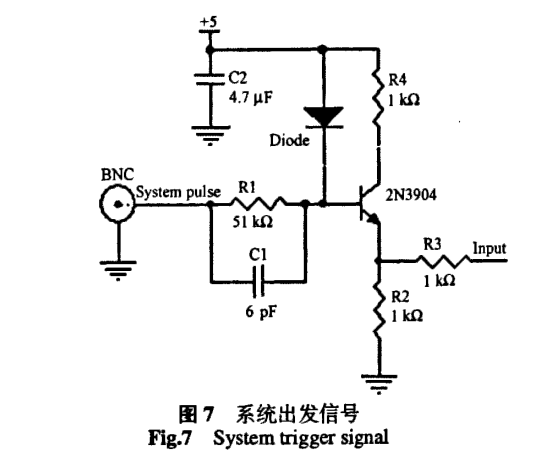

(4)系統觸發信號調節部分:為同步觸發系統信號,尤其是能增加觸發系統的驅動能力。我們採用限幅電路作為電路的啟動信號。電路如圖7。

圖7

圖7系統起始脈衝信號幅度為TTL至10V的脈衝信號。電路中CI是加速電容,能快速地回響啟動信號,產生觸發信號,並能更好地與系統保持同步。

實際電路參數測試結果

(1)本底電平:本底電平是指在輸入信號為零、同步脈衝觸發電路工作的情況下的輸出信號幅度,此時輸出負載為空載。積分時間為0.2、0.4、0.6、0.8和1ms時,本底電平分別為(0~10)、(5~25)、(10~30)、(20~40)和(40~60)mV。

可見無信號輸入時,分時積分器的輸出不為零。這裡的輸出數值系噪聲引起。實驗測量的數據的真實值應滿足:真實值 測量值

測量值 本底電平。

本底電平。

(2)滿幅度輸出電平:滿幅度輸出電平表示積分電路的極限輸出電平,也即積分器連續積分達飽和的值,滿幅度輸出電平 。

。

(3)分時積分器的一致性誤差:對於實際可能工作電路範圍10路分時積分器的一致性誤差 。

。