晶上系統(System on Wafer, SoW)是將不同功能、不同工藝的Chiplet(芯粒)像堆積木一樣組裝和集成到晶圓上,通過復用芯粒可快速組裝成異構、異質、異工藝的大規模複雜系統。

2019年12月,在無錫舉辦CCF第九屆太湖論壇——自主可控大數據與區塊鏈技術大會上,鄔江興院士分析了計算與數據處理面臨的主要挑戰以及計算與微電子技術面臨的挑戰,也介紹了晶圓級處理系統(晶上系統)的概念與優勢,或將成為支撐未來大數據計算的重要解決方案。

基本介紹

基本概念,提出背景,關鍵技術,核心優勢,技術現狀,面臨挑戰,發展趨勢,發展前景,

基本概念

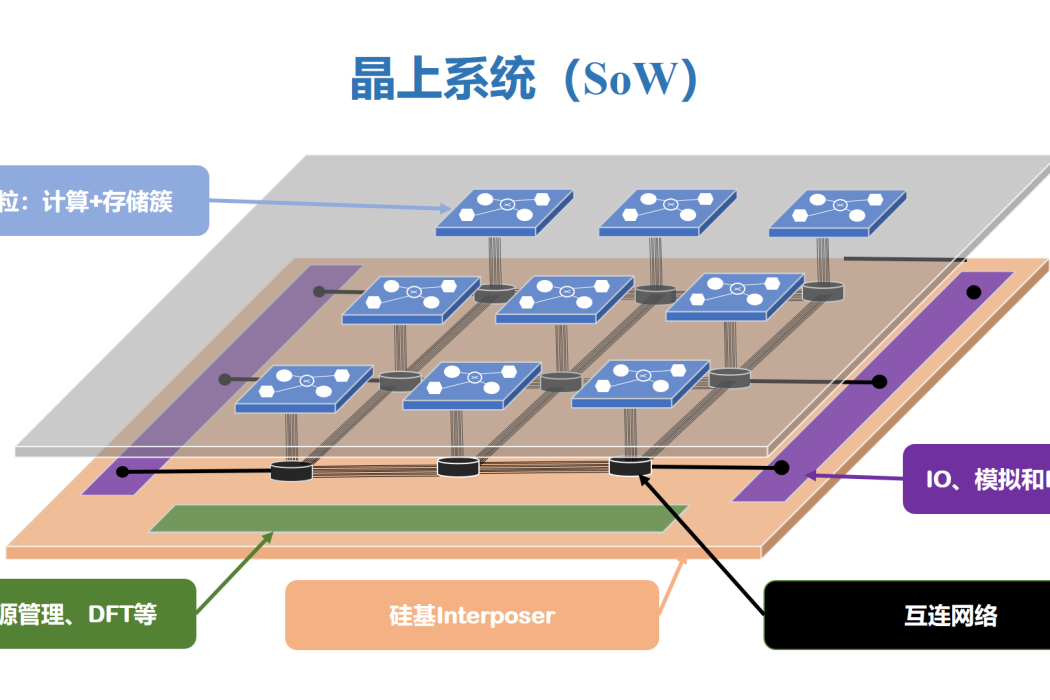

晶上系統(SoW)包含基於晶圓矽基材料的互連集成和晶圓級面積的全利用兩層含義:一方面指基於晶圓母板實現單(多)個Chiplet的互連和封裝,解決現有晶片採用PCB封裝方式的體積大、重量大等問題,實現穿戴、物聯設備等的微型化、輕薄化;另一方面指將多個同構/異構、同質/異質Chiplet互連和封裝成(亞)晶圓尺寸規模的晶片,解決計算、存儲、感測、網路等Chiplet的晶圓級集成封裝,實現超算中心、大數據中心、邊緣計算等系統晶片的低延遲、高頻寬和高能效。 晶上系統形態概念圖

晶上系統形態概念圖

晶上系統形態概念圖

晶上系統形態概念圖提出背景

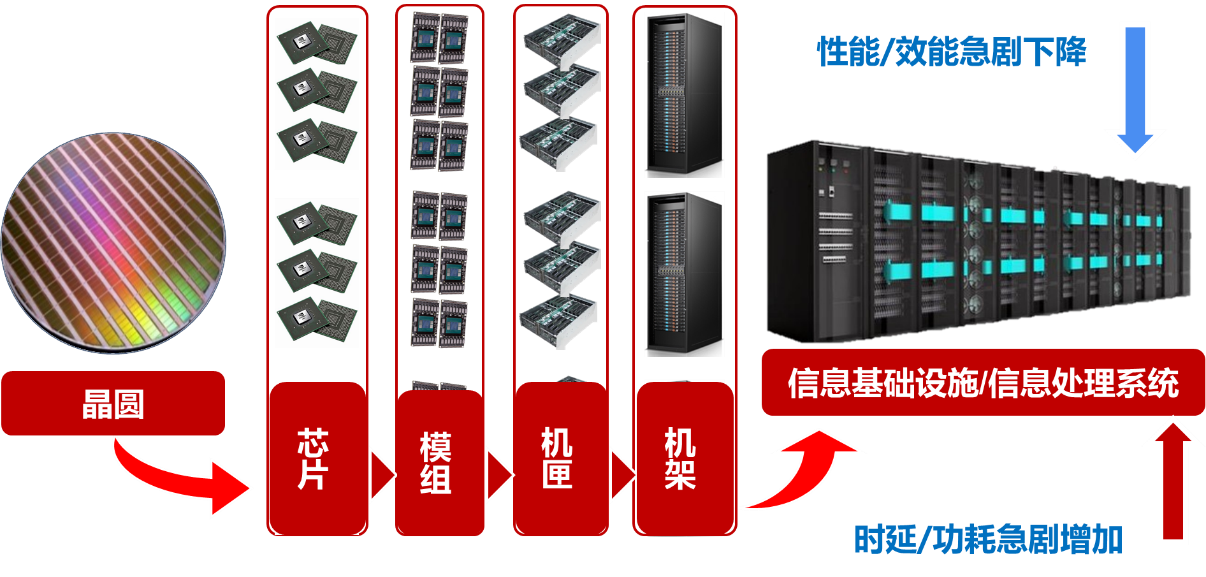

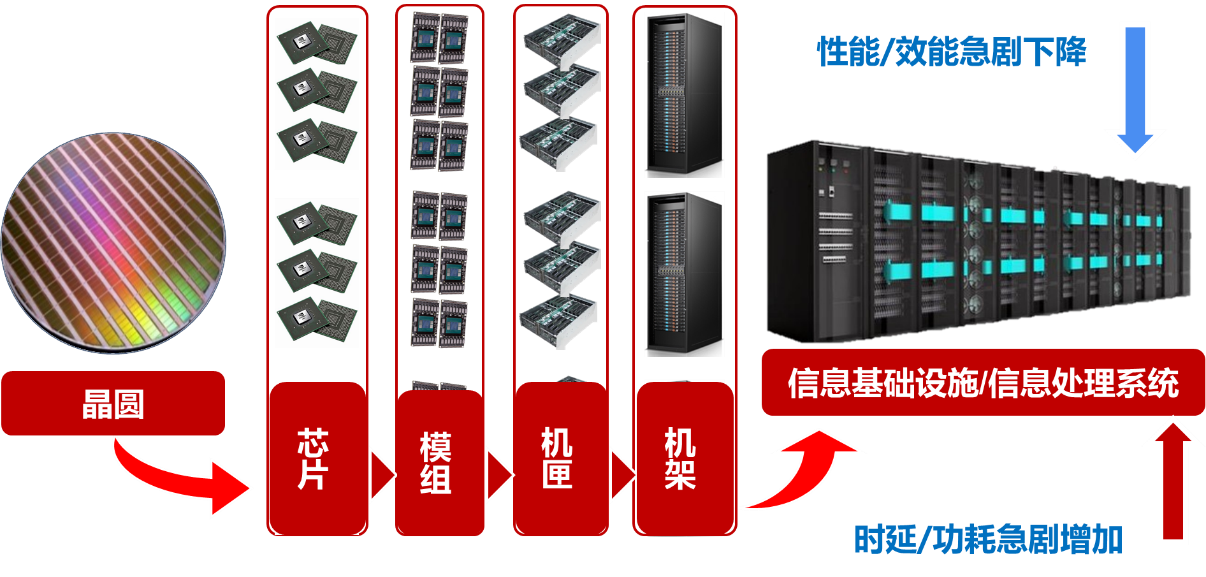

隨著摩爾定律和登納德縮放定律逐漸失效,無論高性能計算機、大型雲服務基礎設施,還是超大規模晶片先進制程工藝等,都陷入了技術和經濟上難以持續發展的困局。信息系統一直遵循“晶片、模組、機匣、機架、系統”的工程實現路線。對信息基礎設施,如超級計算、雲計算、邊緣計算等,為實現服務足夠多的用戶,提供儘可能多的計算、存儲和網路資源,對CPU、DSP、GPU、RAM等不同用途的晶片,往往要層次化的堆疊數萬乃至數十萬規模之巨,功耗和占地極其龐大。更為嚴重的是,這種“拼規模”的模式會導致系統性價比和效能急劇下降,功耗和延遲則會急劇增加,難以持續發展。 基礎設施存在的堆疊發展瓶頸

基礎設施存在的堆疊發展瓶頸

基礎設施存在的堆疊發展瓶頸

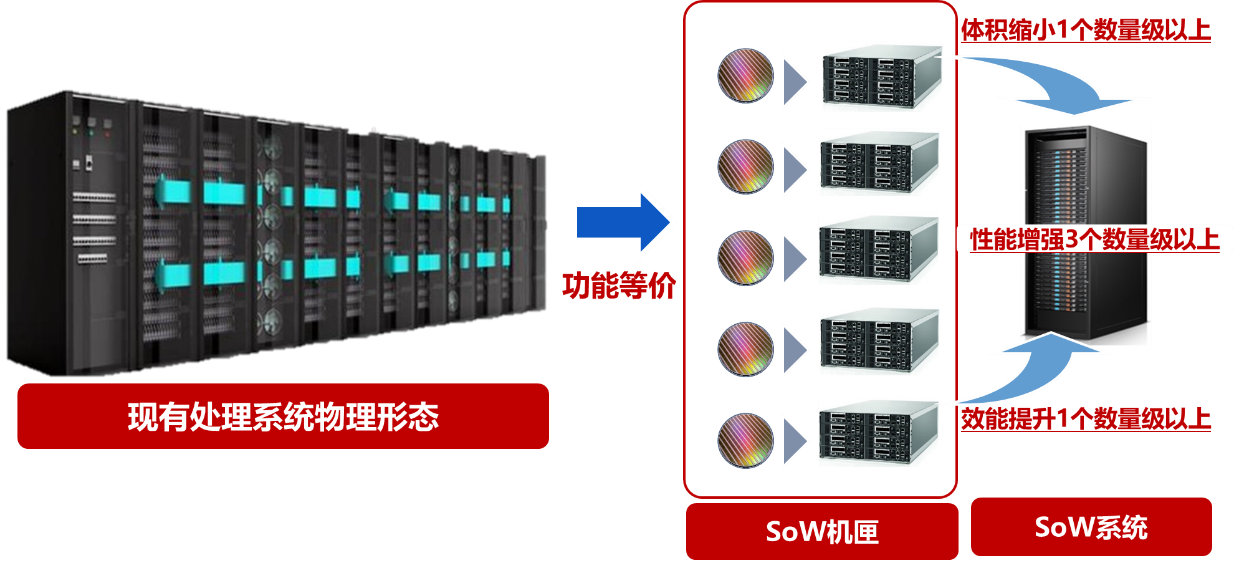

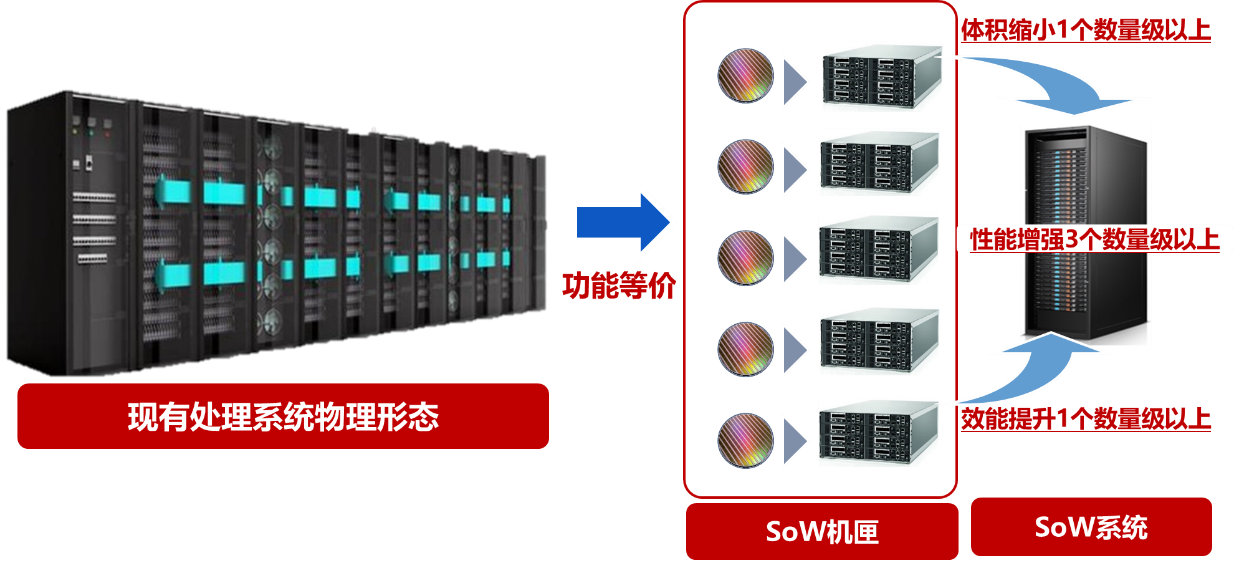

基礎設施存在的堆疊發展瓶頸在這樣的背景下,只有顛覆工程技術路線、打破邊界條件束縛,將SoC升維到晶上系統(SoW),將IP復用提升至芯粒復用,將2D封裝升級至2.5D/3D封裝,將單一工藝拓展至多種工藝,將矽基材料拓展至多種異質材料,藉助晶圓級集成具備的天然高頻寬、低功耗、低延遲、低成本和高密度等連乘增益,可有效破解超大規模晶片和大型信息基礎設施面臨的發展困局,找到可共同持續發展的新基線。 基於SoW改進現有信息處理系統

基於SoW改進現有信息處理系統

基於SoW改進現有信息處理系統

基於SoW改進現有信息處理系統關鍵技術

為了實現靈活、高效的SoW系統,需要體系結構、設計方法、驗證方法、測試方法、流片工藝、封裝工藝和開發工具等體系化創新,具體涵蓋如下新的關鍵技術:

1)領域專用軟硬體協同體系結構

在領域專用軟硬體協同時代,SoW的系統體系結構設計和創新尤為關鍵,體系結構的優劣可直接決定系統的靈活性和效能乃至安全性,也是SoW設計層面最大的技術挑戰。

2)芯粒間互連線口和標準

SoW異構集成系統的芯粒間互連需要統一的接口和遵從相同的標準,如ARM推出的AMBA匯流排業界標準,SoW也需要推出芯粒設計商、代工廠、封裝廠和系統供應商共同遵守的互連標準。需要研製出低延遲、大頻寬、低功耗的大規模晶上互連網路,網路規模是傳統NoC的上千倍,同時具備冗餘特性,能夠應對矽片生產製造的缺陷和性能波動。

3)領域專用多樣化芯粒

從系統套用出發,研究開發多種具有功能可重構、可軟體定義、可相互模組化組裝的KGD(Known Good Die,良die)“芯粒”,如數據存儲、計算、信號處理、數據流管理、模擬電路等“芯粒”。

4)晶圓級高級封裝技術

基於異構芯粒、異構材料和不同工藝的封裝是SoW需要重點突破的關鍵技術,涉及到新工藝、新方法、新工具等方面的支持,以及傳統2.5D和3D集成在SoW技術內涵下的新發展。

5)晶圓級晶片供電技術

晶圓級封裝技術下電流承載能力、長距離傳輸壓降情況、功率損耗和散熱性能都會有新的挑戰,需要研究晶圓級大功率DC/DC供電電路的設計、供電電路與處理器模組的空間布局和集成工藝、影響晶圓級供電穩定性和可靠性的因素和保障辦法等。

6)超高熱流密度散熱技術

針對晶圓級晶片的極高功率密度,需要研究不同種類熱界面接觸材質的傳熱性能、晶片表面強化沸騰結構技術、不同散熱介質對晶片性能的熱穩定性和可靠性影響等。

7)晶圓級晶片開發工具

由於SoW會對晶片的設計、加工、封裝和測試等流程都會帶來全新的影響,因此需要從架構探索,到晶片實現、物理設計提供開發工具的新支持。

8)芯粒和互連網路可靠性技術

對於超大規模的SoW晶片,芯粒和互連網路的可靠性非常重要,需要研究針對芯粒的專門測試和驗證技術,以及矽基互連網路的可靠性工藝及測試驗證技術。

核心優勢

1)功能模組選擇更靈活

通過Die-to-Die連線技術,對連線到底層邏輯晶片的模組晶片原則上沒有限制。例如各類AI加速、GPU、DSP等等模組,可以考慮特點選擇性價比最高的工藝節點進行製造,進一步提升芯粒的靈活性。

2)多元化系統集成維度

SoW晶片一般採用3D集成方案,減小了晶片面積,擴展了空間,這有利於滿足未來智慧型和物聯網市場對領域專用加速部件如AI等的需求,同時可以直接將內生安全作為基本屬性設計進系統,可以實現系統功能增加、性能提升和成本降低。

3)最佳化系統體積功耗指標

基於晶圓集成的互連具有低延遲、低功耗、高頻寬和高密度的特點,可以極大改善不同功能晶片基於PCB板集成的面積、功耗、延遲、頻寬等方面的性能,使得系統的體積、功耗和性能等方面得到極大提升。

4)催生新商業模式

SoW技術會打破現有SoC的晶片產業分工和商業模式,對晶片設計、加工、封裝、測試、模組開發和套用集成的產業分工產生顛覆性的重塑,引發產業的重新洗牌和行業的價值再分配,並催生新的商業模式。

技術現狀

為應對摩爾定律的失效,業界均是從積體電路行業角度探討解決方案,大致按照兩個方向進行了探索,一是發展晶圓級晶片,最早由Gene Amdahl在1980年提出晶圓級集成(WSI)概念,他試圖構建一個晶圓級計算機晶片,並成立創業公司TrilogySystems,受限於當時的工藝條件沒有取得成功。2019年,人工智慧晶片初創公司Cerebras Systems發布世界最大晶片“晶圓級引擎(WSE,Wafer ScaleEngine)”;二是發展三維集成技術,最早起源於20世紀70年代提出的多晶片模組(MCM),而後發展成芯粒(Chiplet)拼裝晶片之路,2017年美國國防部高級研究計畫局(DARPA)啟動通用異構集成和IP重用策略(CHIPS)項目,試圖創建由獨立模組化的、可重用的IP塊組成的全行業生態系統,可以使用現有的和新興的集成技術將這些IP塊組裝到系統中。

面臨挑戰

SoW的發展面臨如下挑戰:

1)互連標準

除了Intel公開了其AIB協定標準,當前各廠商基本上以各家的自有標準為主,後續需要在互連標準方面進行統一,才能成就SoW最大化的復用和組裝生態。

2)封裝技術

在晶圓上集成多個芯粒需要高密度的內部互連線,互連線(微凸)尺寸都將變得更小,這要求互連線做到100%的無缺陷或者提前做好冗餘備份設計。

3)測試技術

採用芯粒模式的SoW晶片必須復用證明功能良好的芯粒,否則會因為單個芯粒的失效影響到SoW晶片整體性能,一旦出現問題損失巨大,因此,需要在芯粒設計中引入滿足SoW組裝的測試接口和測試例。

4)開發工具

不論設計、封裝和測試,都對EDA工具的支持提出了新的功能需求,目前圍繞SoW的開發工具嚴重滯後於發展需求。

發展趨勢

1965 年,戈登摩爾的“把更多元件塞進積體電路里”一直被半導體界奉為圭臬,隨著工藝節點進步,電晶體越做越小、功能越加越多、規模越來越大。但是,“物極必反”,將更多元件塞進積體電路帶來周期長(18~36 個月)、投入大、風險高、面積大、複雜度高、仿真與驗證耗時長,以及重複性和多資源要求等問題,經典的2D縮放已經“耗盡”了現有的技術資源,必須另找出路。

SoW將是工藝節點逼近物理極限、摩爾定律逐漸失效的新出路,不僅可以解決系統對於領域專用多樣化、異質集成多功能等方面的需求,而且還跳出了單一的工藝節點維度來提升晶片的性能,通過芯粒的晶圓級組裝,可以快速、經濟研製出所需要的SoW晶片。而且SoW尤其適用人工智慧、大數據、物聯網等對處理架構、處理範式有創新需求的新興領域,加上SoW可以繼承豐富的功能,可以天然適應當前體系結構的領域專用軟硬體協同設計,可以天然集成內生安全功能與一體,既可以實現高效性、靈活性,又可以獲得天然的內生安全屬性,代表了新一代信息技術產業晶片的發展方向之一。