基本介紹

- 中文名:時分交換的新型FPGA互連結構研究

- 類別:研究

- 類型:時分交換

- 對象:互連結構

中文摘要,外文摘要,

中文摘要

現場可程式門陣列(FPGA)以其獨特的可程式特性、低掩膜成本、快速產品開發、方便產品升級等優勢成為過去二十年中迅速發展的數字系統核心。FPGA的結構決定其獨特的可程式性能,而在大規模FPGA晶片中,可程式互連資源占據整個晶片70%的面積和60%的延時,因此互連資源的結構很大程度上決定了FPGA晶片的性能,是FPGA設計的重中之重。

本文總結了國內外FPGA互連資源的研究現狀,指出傳統互連結構的特點是通過空間上的大量冗餘以滿足實現各種電路連線的靈活性,造成大量互連資源的浪費。隨著FPGA的規模越來越大,傳統互連結構成為提升速度和密度...>> 詳細

本文總結了國內外FPGA互連資源的研究現狀,指出傳統互連結構的特點是通過空間上的大量冗餘以滿足實現各種電路連線的靈活性,造成大量互連資源的浪費。隨著FPGA的規模越來越大,傳統互連結構成為提升速度和密度...>> 詳細

現場可程式門陣列(FPGA)以其獨特的可程式特性、低掩膜成本、快速產品開發、方便產品升級等優勢成為過去二十年中迅速發展的數字系統核心。FPGA的結構決定其獨特的可程式性能,而在大規模FPGA晶片中,可程式互連資源占據整個晶片70%的面積和60%的延時,因此互連資源的結構很大程度上決定了FPGA晶片的性能,是FPGA設計的重中之重。

本文總結了國內外FPGA互連資源的研究現狀,指出傳統互連結構的特點是通過空間上的大量冗餘以滿足實現各種電路連線的靈活性,造成大量互連資源的浪費。隨著FPGA的規模越來越大,傳統互連結構成為提升速度和密度的瓶頸。本文在時分復用、源同步傳輸、串列流水線技術的基礎上,結合通信系統中的時隙交換原理,提出一種新型時分交換FPGA(時分交換即基於時分復用的時隙交換,簡稱TDE-FPGA)的互連結構。這種新型互連結構可以減少互連資源占用晶片的面積、降低設計複雜性、提高可靠性,為開發新型的高邏輯密度、高性能FPGA產品打下基礎。若該研究能在國產FPGA晶片中推廣套用,將為FPGA器件的國產化帶來巨大的社會效益和經濟效益。

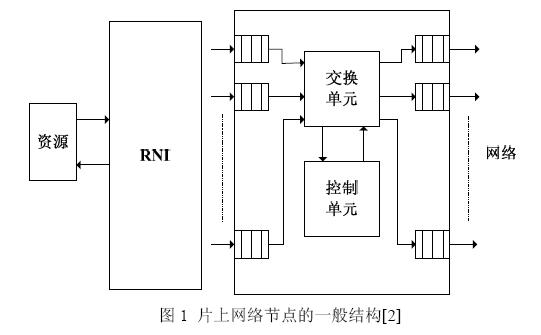

首先提出TDE-FPGA的整體硬體架構:在傳統FPGA的互連資源中添加時隙交換單元、時分復用單元、串化器、解串器等關鍵電路,以支持本文提出的時分交換思想。並採用TSMC 65nm工藝庫對關鍵電路進行仿真,仿真結果證實了TDE-FPGA互連結構的設計思想。

然後將TDE-FPGA中的時分交換互連結構轉換為等價的空間交換互連結構,建立等價參數化空間交換模型,在CAD工具VPR的基礎上改進算法和程式,建立新型TDE-FPGA的軟體模型TDE-VPR。

最後在軟體模型TDE-VPR的基礎上,對TDE-FPGA結構進行評估。將20個MCNC標準測試電路集在TDE-VPR中進行布局布線,比較TDE-FPGA與傳統FPGA結構布局布線成功所需的最小通道寬度數量W〓,結果顯示TDE-FPGA可以減少W〓數量,減少互連資源,提高布通率,而且復用度越高,時分交換的效果越好。並在本文提出的面積評估模型上比較TDE-FPGA和傳統FPGA結構在面積上的差異,結果顯示,新型TDE-FPGA相較於傳統FPGA結構,復用度為8時,最多可節省29.6%的面積,平均最多節省15.2%的互連資源面積。證實使用時分交換的新型TDE-FPGA結構可有效減少互連資源占用晶片的面積。

關鍵字:現場可程式門陣列;可程式互連資源;時分復用;時隙交換;源同步

本文總結了國內外FPGA互連資源的研究現狀,指出傳統互連結構的特點是通過空間上的大量冗餘以滿足實現各種電路連線的靈活性,造成大量互連資源的浪費。隨著FPGA的規模越來越大,傳統互連結構成為提升速度和密度的瓶頸。本文在時分復用、源同步傳輸、串列流水線技術的基礎上,結合通信系統中的時隙交換原理,提出一種新型時分交換FPGA(時分交換即基於時分復用的時隙交換,簡稱TDE-FPGA)的互連結構。這種新型互連結構可以減少互連資源占用晶片的面積、降低設計複雜性、提高可靠性,為開發新型的高邏輯密度、高性能FPGA產品打下基礎。若該研究能在國產FPGA晶片中推廣套用,將為FPGA器件的國產化帶來巨大的社會效益和經濟效益。

首先提出TDE-FPGA的整體硬體架構:在傳統FPGA的互連資源中添加時隙交換單元、時分復用單元、串化器、解串器等關鍵電路,以支持本文提出的時分交換思想。並採用TSMC 65nm工藝庫對關鍵電路進行仿真,仿真結果證實了TDE-FPGA互連結構的設計思想。

然後將TDE-FPGA中的時分交換互連結構轉換為等價的空間交換互連結構,建立等價參數化空間交換模型,在CAD工具VPR的基礎上改進算法和程式,建立新型TDE-FPGA的軟體模型TDE-VPR。

最後在軟體模型TDE-VPR的基礎上,對TDE-FPGA結構進行評估。將20個MCNC標準測試電路集在TDE-VPR中進行布局布線,比較TDE-FPGA與傳統FPGA結構布局布線成功所需的最小通道寬度數量W〓,結果顯示TDE-FPGA可以減少W〓數量,減少互連資源,提高布通率,而且復用度越高,時分交換的效果越好。並在本文提出的面積評估模型上比較TDE-FPGA和傳統FPGA結構在面積上的差異,結果顯示,新型TDE-FPGA相較於傳統FPGA結構,復用度為8時,最多可節省29.6%的面積,平均最多節省15.2%的互連資源面積。證實使用時分交換的新型TDE-FPGA結構可有效減少互連資源占用晶片的面積。

關鍵字:現場可程式門陣列;可程式互連資源;時分復用;時隙交換;源同步

外文摘要

FPGA has become one of the key digital system over the last two decades because of its unique programmable technology, low mask cost, shorten time-to-market and easy to upgrade. The programmable feature of FPGA is decided by its unique architecture. Among the research and development of FPGA architecture, the design of programmable interconnection is the most important, because it costs approximately 70% of the chip area and 60% of the signal delay.

This thesis summarize the research abo...>> 詳細

This thesis summarize the research abo...>> 詳細

FPGA has become one of the key digital system over the last two decades because of its unique programmable technology, low mask cost, shorten time-to-market and easy to upgrade. The programmable feature of FPGA is decided by its unique architecture. Among the research and development of FPGA architecture, the design of programmable interconnection is the most important, because it costs approximately 70% of the chip area and 60% of the signal delay.

This thesis summarize the research about interconnection in FPGA, point out that the traditional fabric gain the flexibility by large redundance in space. As the scale of the chip increase, the traditional fabric soon became the bottle net of speed and density of the chip. This thesis proposed a new architecture of FPGA(Time Division Exchange-FPGA which shorten by TDE-FPGA) interconnect based on time-division multiplex, source-synchronous, pipelining, and the theory of time slot exchange. The new architecture can reduce the area of interconnection resources, play down the design complexity, improve the reliability, lay the foundation for developing high density and low power FPGA chip. It will bring enormous social and economic benefits if the research can be applied in homemade FPGA chips.

Firstly, proposes the whole hardware framework of TDE-FPGA, adds time slot exchange, time division multiplex, serializer and deserializer to the traditional FPGA, and then emulated the added circuits using TSMC 65nm technology library, the results show that the design of TDE-FPGA are thoroughly correct.

Secondly, establish the software model of TDE-FPGA through transport the time division exchange fabric into the space interconnection fabric, based on the CAD tool VPR and modify its arithmetic and procedure, which named TDE-VPR.

Finally, assess the new TDE-FPGA architecture based on TDE-VPR, place and route on TDE-VPR for 20 MCNC standard test circuits, compared the minimal channel width W〓 between the TDE-FPGA and the traditional FPGA. The results show that the TDE-FPGA can reduce the amount of W〓, enhance the routability compared with the traditional FPGA, and with larger M, a better result can be obtained. And then compared the area difference based on the area model, the results show that when M=8, we can save the area of 29.6% at most, 15.2% in average. It proves that the new TDE-FPGA architecture can reduce the area of interconnection resources.

Key Words: Field Programmable Gate Array, Programmable Interconnection, Time Division Multiplex, Time Slot Exchange, Source-Synchronous

This thesis summarize the research about interconnection in FPGA, point out that the traditional fabric gain the flexibility by large redundance in space. As the scale of the chip increase, the traditional fabric soon became the bottle net of speed and density of the chip. This thesis proposed a new architecture of FPGA(Time Division Exchange-FPGA which shorten by TDE-FPGA) interconnect based on time-division multiplex, source-synchronous, pipelining, and the theory of time slot exchange. The new architecture can reduce the area of interconnection resources, play down the design complexity, improve the reliability, lay the foundation for developing high density and low power FPGA chip. It will bring enormous social and economic benefits if the research can be applied in homemade FPGA chips.

Firstly, proposes the whole hardware framework of TDE-FPGA, adds time slot exchange, time division multiplex, serializer and deserializer to the traditional FPGA, and then emulated the added circuits using TSMC 65nm technology library, the results show that the design of TDE-FPGA are thoroughly correct.

Secondly, establish the software model of TDE-FPGA through transport the time division exchange fabric into the space interconnection fabric, based on the CAD tool VPR and modify its arithmetic and procedure, which named TDE-VPR.

Finally, assess the new TDE-FPGA architecture based on TDE-VPR, place and route on TDE-VPR for 20 MCNC standard test circuits, compared the minimal channel width W〓 between the TDE-FPGA and the traditional FPGA. The results show that the TDE-FPGA can reduce the amount of W〓, enhance the routability compared with the traditional FPGA, and with larger M, a better result can be obtained. And then compared the area difference based on the area model, the results show that when M=8, we can save the area of 29.6% at most, 15.2% in average. It proves that the new TDE-FPGA architecture can reduce the area of interconnection resources.

Key Words: Field Programmable Gate Array, Programmable Interconnection, Time Division Multiplex, Time Slot Exchange, Source-Synchronous