抗閂鎖設計技術是指為防止積體電路閂鎖所採用的設計措施。在通常工作條件下,嚴格遵守N阱中的P+有源區與襯底的N+有源區之間距離規則,及N阱和襯底接觸規則,就足夠防止閂鎖。在1/0壓點上,需要增加間距和使用保護環來提高閂鎖能力。

基本介紹

- 中文名:抗閂鎖設計技術

- 外文名:design technology for latchup prevention

- 學科:航空工程

- 領域:工程技術

定義,實例,條件,解決途徑,

定義

抗閂鎖設計技術是指為防止集成電路閂鎖所採用的設計措施。

實例

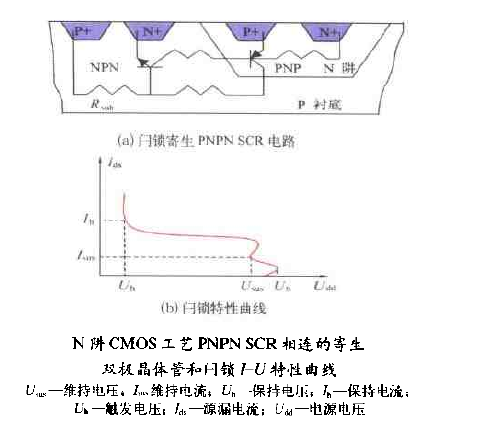

圖1表示了N阱互補金屬氧化物半導體(CMOS)電晶體工藝叫控矽整流器(PNPNSCR)相連的寄生雙極電晶體和閂鎖I— U特性曲線。雙極電晶體要么直接由外界引起開通,要么當阱或襯底中存在明顯電流時由寄生電阻產生壓降而通導。

圖1

圖1條件

引起這種PNPN結構產生閂鎖效應的充分必要條件是:

(1)βmnXβmp>1;βmp,βmn分別為寄生雙極電晶體的兩個放大倍數。

(2) IpRu> 0.7V或InRsub> 0.7V;Ip、Iu分別為雙極電晶體阱內N管激發電流和襯底中的P管激發電流,Ru、Rsab 分別為N阱寄生電阻和襯底中的寄生電阻。

(3)工作電壓必須大於閂鎖維持電壓,而電源能提高的電流大於閂鎖維持電流。

解決途徑

所以解決閂鎖問題的根本途徑是防止上述條件的發生。因此要在下面3個方面減小鎖的激感性:

(1)控制橫向雙極基區寬度;

(2)限制旁路電阻;

(3)用保護環收集注人載流子。

在通常工作條件下,嚴格遵守N阱中的P+有源區與襯底的N+有源區之間距離規則,及N阱和襯底接觸規則,就足夠防止閂鎖。在1/0壓點上,需要增加間距和使用保護環來提高閂鎖能力。