層次化物理設計是指將設計分成數個分割快,然後對每個分割塊進行展平化處理,包括獨立的布局布線等過程,直到完成相應的建模,最後在頂層完成組裝設計。

基本介紹

- 中文名:層次化物理設計

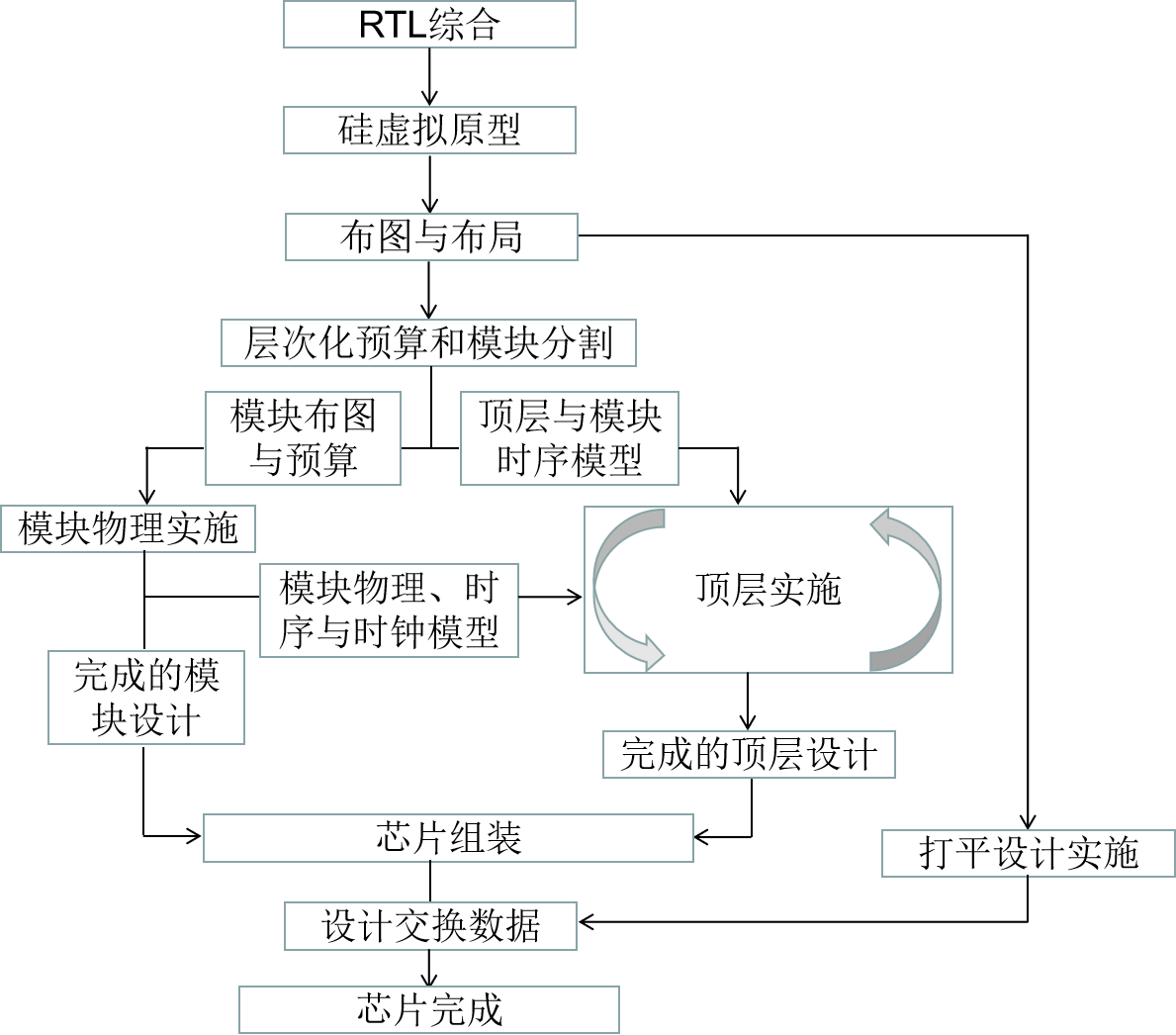

如圖1所示,在設計之初採用矽虛擬原型設計快速的評估性能,然後將其分割成n個物理模組由不同的設計人員並行完成設計,分割後相應的數據包括頂層為n+1組,每組數據包括當前模組的網表(門級netlist和DEF)、物理庫(LEF)、時序庫(.lib)以及分配到模組級的標準時序約束SDC檔案。

圖1 積體電路層次化設計流程

圖1 積體電路層次化設計流程每一個模組的物理設計過程都是一個完整的展平化物理設計過程,它根據頂層分配的物理數據進行物理布圖規劃、布局、布線,經時序最佳化達到時序收斂後,產生滿足物理和時序要求的一組新數據供頂層組裝使用。在做頂層的布圖、布局、布線時,它假定每個模組都是已收斂黑匣子,其物理布圖最終覆蓋在n個物理模組的上方,並占據整個晶片的面積範圍。當最終頂層的時序及最佳化達到要求時,整個設計完成。

層次化物理設計方案的最大優點是它將很大的設計化成多個小設計,如果有時序問題可能存在於個別模組,再去重點解決,則複雜性變小,而且是局部的。同時每個工程師分擔的工作量也變小,完成設計的時間周期會縮短,從而加快了設計收斂。如果某些模組(如時序)不能達到要求,在頂層再做時序調整或重新分割,也可以局部採用物理綜合。