基本介紹

- 中文名:前道工序

- 外文名:Front end of line

- 英文縮寫:FEOL

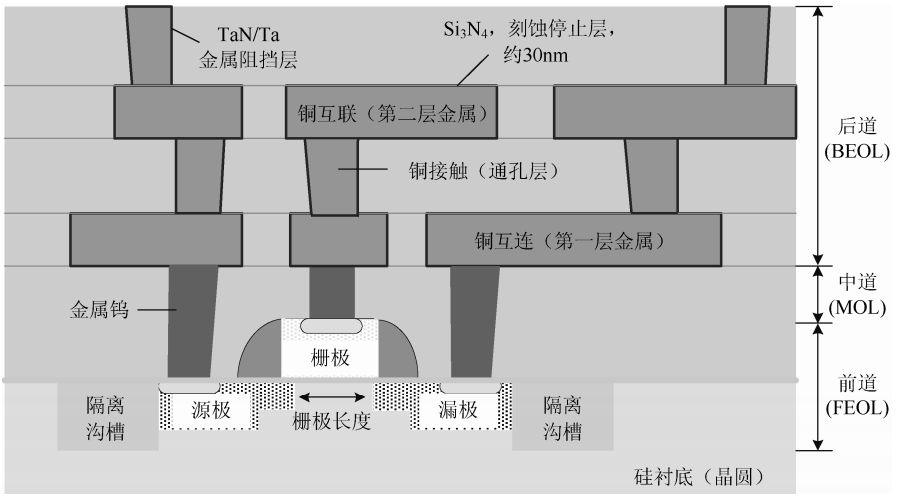

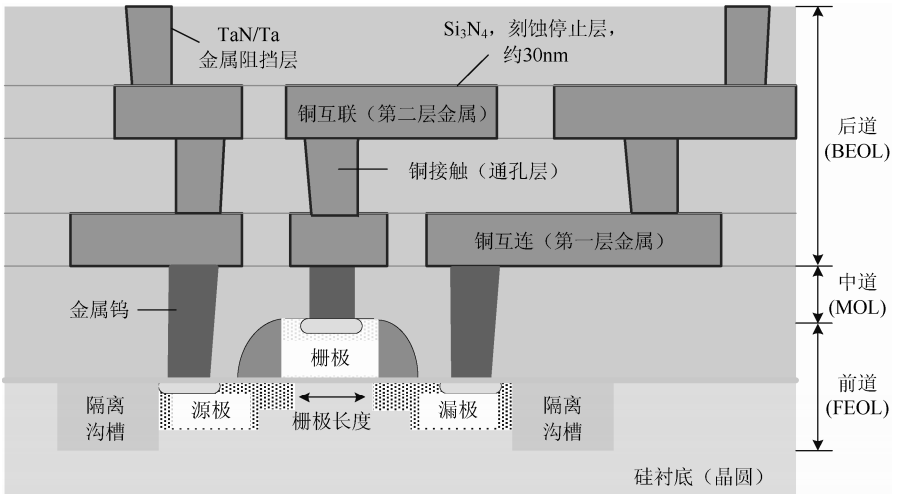

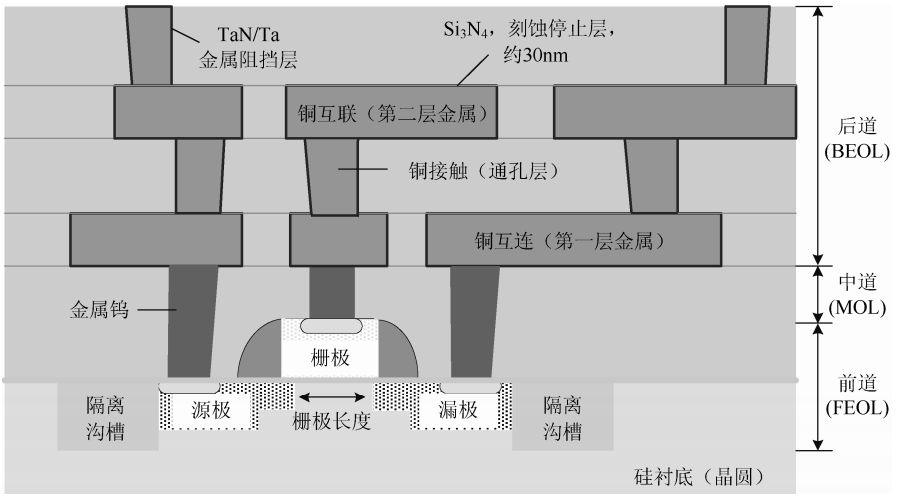

圖1是一個邏輯器件的剖面示意圖。新的集成技術在晶圓襯底上也添加了很多新型功能材料,例如:前道(FEOL)柵極的高介電常數材料,它能有效地增大柵極的電容並減少漏電流。前道(FEOL)中的關鍵光刻層是 FIN 和柵極(gate)。後道(BEOL)的關鍵光刻層是 V0/M1/V1/M2,其中V0/V1是通孔層,M1/M2是金屬層。

圖1 一個邏輯器件的剖面示意圖

前道工藝編輯 鎖定 積體電路是依靠所謂的平面工藝一層一層製備起來的。對於邏輯器件,簡單地說,首先是在 Si襯底上劃分製備電晶體的區域(active area),然後是離子...

前道工序是指製衣的前道工序,是為後一道工序做好充分準備的工作內容。...... 前道工序是指製衣的前道工序,是為後一道工序做好充分準備的工作內容。...

工藝絲綢染整,絲綢的生產過程中具有重要的地位,主要包括生絲及織物的精煉、染色、印花和整理四道工序。...

(1)當前道工序的單間作業時間小於或等於後道工序的單間作業時間時,則前道工序上完工的每一個零件應立即轉移到後道工序去加工,即按平行移動方式單件運輸。...