簡介 光接收機前端作為光纖通信系統的重要組成部分,其性能指標直接決定著光接收機的整體性能。由於基於標準 CMOS 工藝的光接收機成本低廉、市場套用前景廣闊,近年來引起極大關注,並取得飛速的進展。本文首先回顧了基於標準 CMOS 工藝光電探測器的基本結構,以及跨阻放大器的核心電路,重點總結了標準 CMOS 工藝中光接收機的最新研究進展。

背景 伴隨著信息通信技術的廣泛套用和各種新業務的不斷湧現, 在全球網路數據量飛速增長的同時,個人對網路頻寬的需求也日趨顯著。據網際網路數據中心 IDC 的研究報告, 2011 年全球數據總量達 1.8ZB (1ZB=270Byte), 2015 年將達 8ZB。如此海量信息的傳輸和交換必須實現高速化,因而對頻寬、碼間干擾等提出了更高的要求。由於受 RC 時延的影響,傳統的基於銅互連的信息傳輸技術難以實現。近年來,隨著集成光學和集成光電子技術的不斷進步, FTTx[2,3]、車/機內通信[4]、板/片間互連[5,6]等短距離和甚短距離通信都可採用單片或混合集成的光互連技術來實現。與銅互連相比,光互連具有極高的時間空間頻寬積、高速、高密度、無干擾、傳輸功耗低等優點,因而成為已開發國家重點研究開發的一項新技術。

由於標準 CMOS 工藝具有廉價、可批量生產、成品率高等優點,在標準 CMOS 接收電路晶片上集成光電探測器可最大限度地消除互連、引線和封裝等寄生參量影響,提高光接收機的整體性能,同時還具備體積小、成品率高、可靠性好、可實現更為豐富功能的優點。近年來,隨著不斷提升。如何基於標準 CMOS 工藝實現光電探測和放大/處理電路的單片集成,成為光電集成領域的研究熱點。

分類 按光檢測器的種類,光接收器集成可分四類:①PIN/FET光接收器適合1.1~1.6μm光纖通信;②光電導檢測器(PCD)/FET光接收器,適用接收0.8μm波段的光纖通信;③MSM/FET光接收器,MSM由兩個背靠背肖特基結組成,與FET工藝相容,易於大規模單片集成。已製成四個MSM與8 000支FET集成在同一GaAs基片上,它能快速檢測和處理數據;④異質結光電晶體(HPT)/HBT(異質結雙極電晶體)光接收器,其成本低,但工作速率也低。圖1為最通用的PIN/FET混合集成光接收器模組電路圖。用PIN光電二極體接收光信號後,用低噪聲FET作前置放大,再用三個雙極電晶體組成放大電路以提高探測靈敏度。典型參數值:電流靈敏度為0.8A/W;上升回響時間為50ps;下降時間為55ps;漏電流為3nA;結電容為0.3pf。

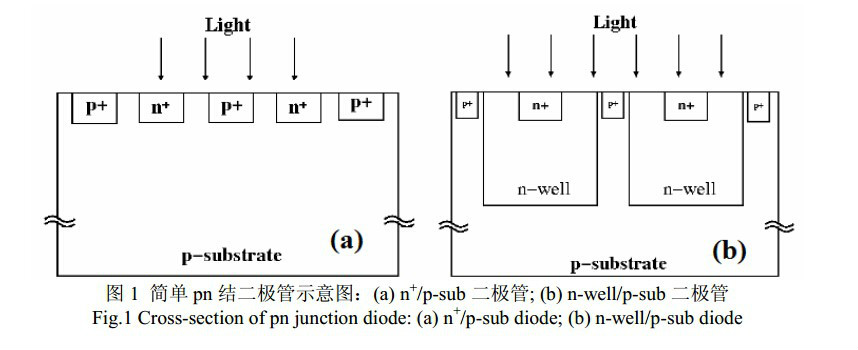

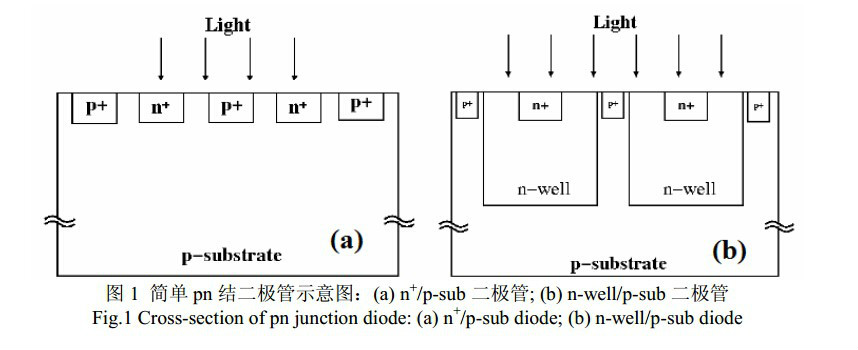

圖1 PIN/FET 混合集成光接收器模組電路圖 光電檢測器 光電探測器位於光接收機的最前端,其參數直接影響著光接收機的整體性能。目前在標準 CMOS 工藝中實現的探測器主要基於 pn 結和肖特基結,常用結構有 n+/p-sub 二極體、n-well/p-sub 二極體、 p+/n-well/p-sub 雙光電二極體、空間調製光探測器、 MSM 光電探測器及光電電晶體。最簡單的光電探測器是反向偏置的 n+/p-sub 二極體,如圖 1(a)所示[7]。由於 n+結淺,耗盡區窄,因而對光生載流子的收集效率低。為了提高回響度,可以採用如圖 2(b)所示的n-well/p-sub 二極體[7,8]。與圖 2(a)相比, pn 結更深、耗盡區更寬,因而有利於光生載流子的收集。

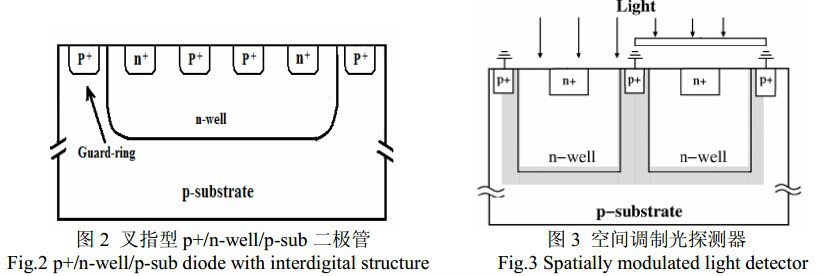

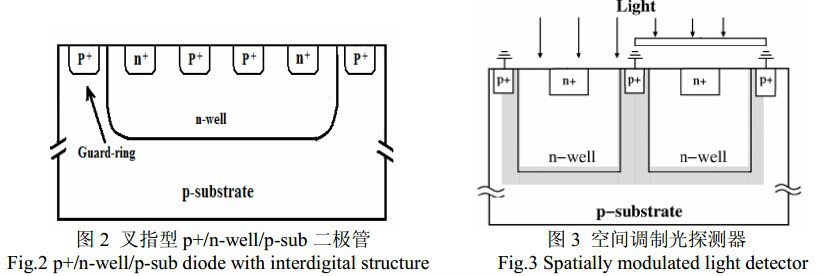

圖2 簡單pn結二極體示意圖 上述 pn 結探測器雖然結構簡單, 但在襯底深處產生的光生載流子需擴散到探測器電極,因而在脈衝回響中引入拖尾,限制了探測器的回響速度。為了消除拖尾效應,文獻[9,10]提出了利用 p+/n-well/p-sub 結構的雙光電二極體,如圖 3 所示。其中,叉指型 p+區與 n 阱形成工作二極體, n 阱與 p 襯底形成禁止二極體。當探測器處於工作狀態時,工作二極體和禁止二極體均處於反偏狀態,因而在襯底深處產生的慢擴散光生載流子被禁止二極體吸收,從而消除了襯底慢擴散載流子對工作二極體回響速度的限制。此外,該結構還利用叉指型 p+區使工作二極體的耗盡區最大化,有利於光生載流子收集,進一步提高了光電探測器的速度和回響度。 2007 年, Yu C L 等人[11]採用 CSMC 0.6μ m CMOS 工藝,製備了面積為40μm× 40μm的雙光電二極體,測試結果表明, -3dB 頻寬可達 1.1GHz,然而,回響度偏低,僅為0.04A/W。

圖3 光接收器 另一種緩解慢擴散載流子效應的結構是空間調製光(Spatially-Modulated Light, SML)探測器 [12-14]。它由受光的瞬時二極體和禁止光的延遲二極體構成,利用二者的光電流回響差來消除襯底深處產生的慢擴散載流子效應,從而提高光電探測器的物理頻寬和速度,其基本結構如圖 3 所示。其中, n-well 與 p 襯底構成瞬時二極體,而標準 CMOS 工藝中的 M2 與n-well/p-sub 一起構成延遲二極體。通過版圖布局的格線化設計,可獲得的-3dB 頻寬最大可達 1.1GHz,比傳統 n-well/p-sub 二極體的頻寬提高了兩個數量級。

雖然基於 pn 結二極體的光電探測器取得了較高的頻寬,但頻寬的提高是以犧牲回響度為代價的。在某些高靈敏度套用場合下,探測器的回響度可能更為重要。文獻[7]提出了一種基於標準 CMOS 工藝的寄生光電電晶體作為光接收機的探測器,如圖 4 所示。當 p 型基區空置,深 n 阱集電區與 n+發射區正向偏置時,在基區內產生的光生載流子被電晶體放大,因而可實現高靈敏度探測。 基於 65nm CMOS 工藝製備的 npn 光電電晶體的直流回響度可達0.34A/W[7],不幸的是,頻寬僅為 0.15MHz。這是因為光電電晶體是 CMOS 工藝中的寄生器件,基區較厚且摻雜剖面未經最佳化造成的。

跨阻放大器 提高光接收機靈敏度的方法除了提高探測器的回響度, 還需降低前置放大器的輸入噪聲電流。由於跨阻結構放大器在噪聲和頻寬方面具有很好的折衷,因此,在高速、高靈敏度套用場合倍受青睞。目前,學者採用的跨阻放大器核心電路主要有調節型共源共柵(RGC)放大器、有源反饋跨阻放大器和零極點對消跨阻放大器等。

RGC 放大器屬於電流模形式的跨阻放大器,它是一種利用共柵電路或共源共柵電路自身特性形成電流輸入、電壓輸出的跨阻放大器。因為不需要添加額外的反饋電阻,在一定程度上緩解了增益、頻寬和噪聲之間的矛盾,提高了跨阻放大器的整體性能。該放大器具有輸入阻抗小、頻頻寬及電壓擺幅好的特點。 2004 年, Park S M 等人[16]首次將 RGC 結構(圖 6)套用於光接收機前端電路中,並成功地實現了 1.25Gb/s 的傳輸速率。

單片集成 CMOS 光接收機的研究進展 由於矽基標準 CMOS 工藝的單片光電集成接收機具有成本低、可批量生產、成品率高120 等優點,成為集成光電子領域的研究熱點,並取得了飛速的發展。自 1999年Bell 實驗室首次報導了基於標準 CMOS 工藝的光電集成接收機後[9],各已開發國家的研究人員對此進行了積極的探索。比利時 K U Leuven 大學的 Hermans C 等人[18,19]從2000 年開始對基於標準 CMOS 的光電探測器、光接收電路及單片集成光接收機進行了廣泛的研究。 2006 年,該研究小組採用 0.18 µm 標準 CMOS 工藝研製出工作波長 850 nm 的傳輸125 速率 1.2 Gb/s、靈敏度–8 dBm 的單片集成接收機[19]。德國斯圖加特大學的 Jutzi M 等人對集成差分探測器和空間調製光探測器的光接收機前端進行了研究, 2006 年報導了一種基於標準 CMOS 工藝集成 SML 探測器的 2Gb/s 單片集成光接收機[20]。另外,荷蘭 Twente 大學的Radovanovic S 等人[21]對標準 CMOS 工藝中的高速探測器進行了系統的研究,首次提出採用模擬均衡器補償探測器的光頻回響來實現高速、高靈敏度的光電集成接收機。 2005 年,該130 研究小組基於 0.18 µm 標準 CMOS 技術研製出了一種工作波長 850 nm、傳輸速率 3 Gbit/s、靈敏度達-19 dBm的單片光電集成接收機。

國內研究現狀 與國外研究相比,國內對基於標準 CMOS 工藝單片集成光接收機的研究相對遲緩。近年來,中科院半導體所、東南大學、天津大學等多家單位對標準 CMOS 工藝光接收機的前置放大器、光互連、單片集成等方面進行了積極的探索。如東南大學射光所在 CMOS 光接145 收機前置放大器方面做了深入的研究 [26,27],中科院半導體所在光互連方面取得較大進展。 天津大學新型器件與集成技術實驗室在單片集成光接收機晶片研製方面取得較大突破。2009 年,採用 Charted 0.35μ m EEPROM CMOS 工藝集成了差分探測器、差分跨阻放大器及限幅放大器,實現 1.5Gb/s@10-9 的傳輸速率。2011 年,利用 EEPROM 工藝中的肖特基接觸,設計了單片集成 MSM 探測器的光接收機[15],如圖 9 所示,採用有源反饋和150 負米勒反饋電容的跨阻放大器來拓展頻寬。 在 Charted 0.35μ m EEPROM CMOS 工藝下實現了頻寬為 1.7GHz 的光接收機,在-15dBm 光功率和 10-9 誤碼率條件下,可完成 2Gb/s的數據傳輸。

圖1 PIN/FET 混合集成光接收器模組電路圖

圖1 PIN/FET 混合集成光接收器模組電路圖 圖2 簡單pn結二極體示意圖

圖2 簡單pn結二極體示意圖 圖3 光接收器

圖3 光接收器 圖1 PIN/FET 混合集成光接收器模組電路圖

圖1 PIN/FET 混合集成光接收器模組電路圖 圖2 簡單pn結二極體示意圖

圖2 簡單pn結二極體示意圖 圖3 光接收器

圖3 光接收器