主時鐘是產生準確定時信號用以控制其他時鐘及可能還有設備的時鐘;在國內數字網中,在由單一參考時鐘控制所有時鐘以取得完全同步網的情形,這個控制時鐘一般稱為主時鐘,

| 中文名稱 | 主時鐘 |

| 英文名稱 | master clock |

| 定 義 | 用於控制其他時鐘頻率的時鐘。 |

| 套用學科 | 通信科技(一級學科),支撐網路(二級學科) |

基本介紹

- 中文名:主時鐘

- 外文名:master clock

- 定義:用於控制其他時鐘頻率的時鐘。

- 套用學科:通信科技,支撐網路

定義

最佳主時鐘算法

系統主時鐘

組成單元

時鐘源的選擇

鎖相環

主時鐘是產生準確定時信號用以控制其他時鐘及可能還有設備的時鐘;在國內數字網中,在由單一參考時鐘控制所有時鐘以取得完全同步網的情形,這個控制時鐘一般稱為主時鐘,

| 中文名稱 | 主時鐘 |

| 英文名稱 | master clock |

| 定 義 | 用於控制其他時鐘頻率的時鐘。 |

| 套用學科 | 通信科技(一級學科),支撐網路(二級學科) |

主時鐘是產生準確定時信號用以控制其他時鐘及可能還有設備的時鐘;在國內數字網中,在由單一參考時鐘控制所有時鐘以取得完全同步網的情形,這個控制時鐘一般稱為主時鐘,...

時鐘頻率(又譯:時鐘頻率速度,英語:clock rate),是指同步電路中時鐘的基礎頻率,它以“若干次周期每秒”來度量,量度單位採用SI單位赫茲(Hz)。它是評定CPU性能的...

《主題時鐘鬧鐘》是一款IOS平台的套用。... 在有限的時間內免費 主題時鐘,多報警終於來到了在App Store ! 它有百日咳12夢幻般的原始的時尚主題,你不會找到任何...

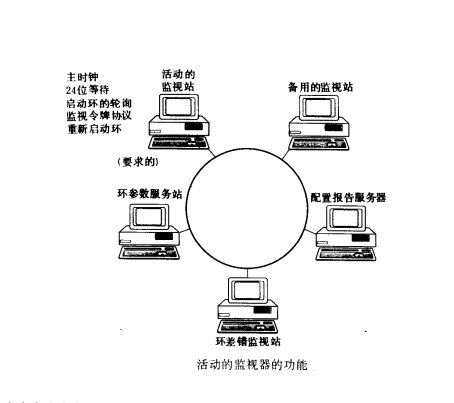

精確時鐘同步協定(IEEE1588)是關於網路測量和控制系統的時間協定,可達到較高的網路對時精度,實現高精度的時間同步。最佳主時鐘算法(BMC)是IEEE1588的最主要的核心...

《時鐘機關之星》是由日本輕小說家榎宮祐和暇奈椿共同著作,插畫家茨乃負責插畫,講談社輕小說文庫出版的輕小說。該輕小說由兩位作者“合作”而成,形式十分罕見。本作...

在單片機程式設計中,設定一個好的時鐘中斷,將能使一個CPU發揮兩個CPU的功效,大大方便和簡化程式的編制,提高系統的效率與可操作性。可以把一些例行的及需要定時...

體育場館主計時時鐘系統 給體育館內重要區域提供可靠、經濟和有效,能夠提供一個統一的、標準的全場時間。...

《命運時鐘之命運之主》是黑色南君創作的網路小說,發表於起點網。... 《命運時鐘之命運之主》是黑色南君創作的網路小說,發表於起點網。中文名稱 命運時鐘之命運...

(時鐘機關之星女主角之一)編輯 鎖定 討論 編號Initial-Y04 “擊滅者”安可兒,琉珠的妹妹。由Y製作的Y系列四號機。中文名 安可兒 外文名 アンクル 登場...

這是一本以白雪、小美人魚、灰姑娘、貝兒、愛洛六位迪士尼公主為主角的時鐘書,共10頁。這本時鐘書造型新穎獨特,中心是一個直徑為18厘米的大錶盤,錶盤上有兩個...

《鎖屏主題星耀時鐘》是一款Android平台的套用。... 鎖屏主題星耀時鐘支持版本 編輯 2.0及以上固件版本參考資料 1. 鎖屏主題星耀時鐘 .下載連結[引用日期2015-01-27...

《迪士尼造型時鐘:美麗的公主》以迪士尼中的經典人物形象米奇妙妙屋、公主和賽車為主題,與認知時間、數字和形狀相結合。讓小朋友通過簡單的動手來來更好的掌握對鐘錶...

主從同步是在一個交換節點設立一高精度的基準時鐘,通過傳輸鏈路把此基準時鐘信號送到網中各個從節點,各個從節點利用鎖相環技術把本地時鐘頻率鎖定在基準時鐘頻率上...

電腦主頻率,簡稱主頻,每一台 電子計算機的中央處理器中均有 一個不斷地按固定頻率產生時鐘脈衝信號的裝置,這個裝置叫脈衝信號源,或叫主時鐘,它所產生的頻率就是...

主從觸發器由主觸發器和從觸發器組成,且兩個觸發器的邏輯功能和同步RS觸發器的邏輯功能完全相同,時鐘信號CP經由非門,變成CP’控制從觸發器。當CP=1時,CP‘=0,...

主從同步網是指從節點的時鐘受主節點基準時鐘控制的“同步 網”。目前得到廣泛套用的一種同步網。在主節點 設立由銫原子鐘組成的高精度基準時鐘,通過傳輸 鏈路把...

館內外規劃有呈現六大主題區塊:時間主題廣場、鐘錶文化展館、鐘錶工匠部落、鐘錶DIY互動體驗區、特色主題展售區、時光主題餐廳。 (一)時間主題廣場:...