《中央處理器或微控制器的數據相關判別及選擇傳遞電路》是杭州華盛微電子有限公司於1999年12月13日申請的專利,該專利的申請號為991242432,公布號為CN1300005,公布日為2001年6月20日,發明人是謝衛國、嚴曉浪、滕強華,該發明涉及精簡指令集流水線結構的中央處理器(CPU)或微控制器(MCU)。

《中央處理器或微控制器的數據相關判別及選擇傳遞電路》所述數據相關判別電路包括兩個地址比較器,分別用於把讀運算元階段及執行階段的指令中的運算元地址與寫結果階段的指令中的目標地址進行比較,數據選擇傳遞電路根據數據相關判別電路的比較結果把來自微控制器中的累加器、隨機存取存儲器、指令解碼器。寫結果暫存器和數學邏輯單元的選擇性地輸出到數學邏輯單元。

2007年,《中央處理器或微控制器的數據相關判別及選擇傳遞電路》獲得第五屆江蘇省專利項目獎優秀獎。

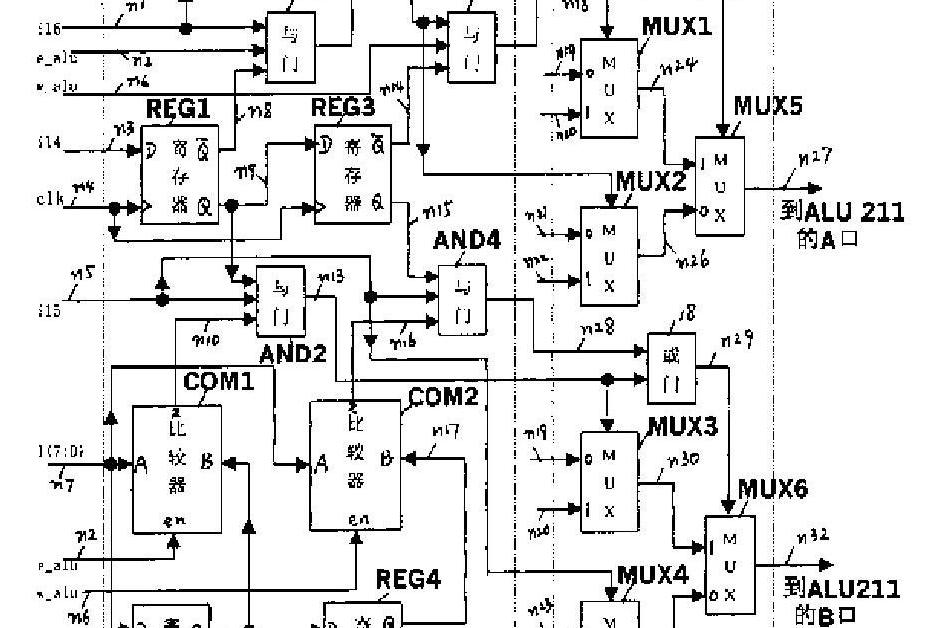

(概述圖為《中央處理器或微控制器的數據相關判別及選擇傳遞電路》摘要附圖)

基本介紹

- 中文名:中央處理器或微控制器的數據相關判別及選擇傳遞電路

- 公布號:CN1300005

- 公布日:2001年6月20日

- 申請號:991242432

- 申請日:1999年12月13日

- 申請人:杭州華盛微電子有限公司

- 地址:浙江省杭州市文二路385號805室

- 發明人:謝衛國、嚴曉浪、滕強華

- 分類號:G06F9/28

- 代理機構:上海專利商標事務所

- 類別:發明專利

- 代理人:張政權

專利背景,發明內容,專利目的,技術方案,改善效果,附圖說明,權利要求,實施方式,榮譽表彰,

專利背景

在現代微電腦晶片設計中,精簡指令集流水線結構越來越流行,採用流水線結構的目的是提高執行速度。現舉例來說明。在一定的工藝技術條件下,如果一個微電腦晶片執行一條指令所需的平均時間為1微秒,若不採用流水線結構,則其執行速度為平均1條指令/1微秒;若採用4階段的流水線結構,則其執行速度為平均4條指令/1微秒。現以4階段流水線結構為例來說明精簡指令集流水線結構微控制器的工作原理。

參考圖1來說明精簡指令集流水線結構微控制器的工作原理。

第一階段,取指令階段(IF階段):程式計數器101提供一個地址P1給指令唯讀存儲器102。指令唯讀存儲器102將輸出一條與此地址相對應的指令向量P2。該指令向量包括運算元或運算元地址、目標地址及操作控制碼等。

第二階段,讀運算元階段(RD階段):指令向量P2經指令暫存器103延時一個時鐘周期後通過該暫存器103的輸出端103a傳送給指令解碼器105。該解碼器105將輸入的指令向量解碼後輸出各種微代碼向量P7、P8、P9、P10、P11等。向量P7、P8分別為兩個運算元的地址。根據這些運算元地址,從隨機存取存儲器(RAM)107中取出相應的運算元P13、P14,並輸送到數據選擇傳遞電路109的輸入端。數據選擇傳遞電路109根據來自數據相關判別電路108的控制向量P15,選擇兩個適當的運算元並通過其輸出端P16、P17輸送給數學邏輯單元111。

第三階段,執行運算階段(EX階段):數學邏輯單元(ALU)111根據操作控制代碼P11,對運算元P16、P17進行相應的操作運算,並將運算結果通過其輸出端111a輸送給寫結果暫存器106。

第四階段,寫結果階段(WR階段):將存在寫結果暫存器106中的運算結果通過其輸出端106a寫入到RAM107中。

上述四階段流水線結構的操作可用下表一來觀察。

在周期0,指令1在取指令階段,此時指令1已從指令存儲器102中取出。在周期1,指令1移到讀運算元階段,根據指令1中規定的地址,讀取運算元A、B。此時,指令2進入取指令階段。在周期2,指令1進入執行階段,將操作碼提供給數學邏輯單元111並將執行規定的操作運算;指令2移到讀運算元階段,指令3進入取指令階段。最後,在周期3,指令1進入寫結果階段,將數學邏輯單元111的運算結果寫入到目標地址規定的存儲單元中。

周期 | 取指令階段 | 讀運算元階段 | 執行階段 | 寫結果階段 |

0 | 指令1 | |||

1 | 指令2 | 指令1 | ||

2 | 指令3 | 指令2 | 指令1 | |

3 | 指令4 | 指令3 | 指令2 | 指令1 |

4 | 指令5 | 指令4 | 指令3 | 指令2 |

從上述流水線圖表中,可以看到,指令2與3中的運算元正在或已被讀取時,指令1的結果被寫入到存儲單元中。如果指令2與3在讀運算元或執行指令的階段需要用指令1的運算結果,那么指令1的運算結果就必須被提前傳遞到數學邏輯單元111的輸入端,否則,就會發生“數據災難”(DATA HAZARD)或得到錯誤的結果。例如,若指令2要用指令1的結果,那么在周期3,指令1的結果在被寫入存儲器的同時必須被向前轉送到指令2的執行階段。(這種數據轉送是通過下列方法來實現的:將讀運算元階段和執行階段的運算元地址或位置與寫結果階段的目標地址或位置進行比較,並用一組多路選擇開關將適當的運算元據傳遞給數學邏輯單元111。

考慮下列程式片段: | ||||

SUB | A,B,C | ---- | A-B, | 結果存放到C |

ADD | D,C,F | ---- | D+C, | 結果存放到F |

指令X | ||||

指令Y | ||||

上述程式片段的執行次序可用下表二的流水線圖表來表示。

周期 | 取指令階段 | 讀運算元階段 | 執行階段 | 寫結果階段 |

0 | SUB A,B,C | |||

1 | ADD D,C,F | SUB A,B,C | ||

2 | 指令X | ADD D,C,F | SUB A,B,C | |

3 | 指令Y | 指令X | ADD D,C,F | SUB A,B,C |

在周期3中,A-B的結果被寫入C。可是在執行階段,C卻被用來計算D+C。因此,正常的讀運算元路徑必須被繞開,並必須將寫結果階段中的C值傳遞到執行階段的數學邏輯單元的輸入端。否則,就得不到預期的結果。

在複雜指令集微控制器中,由於相鄰指令的執行在時間上是互不重疊的,即在當前這條指令執行完畢之後,下一條指令才被從指令存儲器中取出並開始執行。但在精簡指令集流水線結構微控制器中,由於相鄰指令的執行在時間上是相互重疊的,如果某一條指令的運算元是相鄰前一條或二條指令的執行結果(這種情況稱為數據相關),那么就必須將這一個結果向前傳遞到執行階段,否則,就會發生所謂的“數據災難”(Data Hazard),也就不可能得到期望的運算結果。為了實現各階段之間數據的正確傳遞,需要將讀運算元階段的指令和執行階段的指令中的運算元地址與寫結果階段的指令中的目標地址進行比較;然後用比較的結果所產生的信號來控制一組多路選擇開關,從而將適當的運算元傳送到數學邏輯單元的數據輸入口。為了準確無誤地實現這種數據傳遞,就必須要用數據相關判別電路來判別相鄰指令是否具有數據相關性。

1999年12月前,在普通的精簡指令集流水線結構的控制器中所用的數據相關判別電路中,需要用4個地址比較器再加上其它邏輯組合及時序電路。

發明內容

專利目的

《中央處理器或微控制器的數據相關判別及選擇傳遞電路》提出了一種新的指令數據相關判別電路,在該電路中,只用了2個地址比較器,其餘部分的電路也比過去的技術簡單。

該發明的目的在於簡化電路,提高可靠性,並縮小晶片面積,降低生產成本。該發明設計的4階段流水線結構微控制器中數據相關判別電路僅採用2個地址比較器,而過去的技術需要用4個地址比較器。

該發明提出了一種新的套用於流水線結構微控制器或中央處理器的數據相關判別及選擇傳遞電路。

該發明提供了一種新的精簡指令集流水線結構的微控制器,該微控制器包括一數據相關判別電路和一數據選擇傳遞電路,其中數據相關判別電路包括第一和第二地址比較器,第一地址比較器用於把微控制器的讀運算元階段的指令中的運算元地址與寫結果階段的指令中的目標地址進行比較,第二地址比較器用於把微控制器的執行階段的指令中的運算元地址與寫結果階段的指令中的運算元地址進行比較,數據選擇傳遞電路用於根據數據相關判別電路的比較結果把來自微控制器中的累加器、隨機存取存儲器、指令解碼器、寫結果暫存器和數學邏輯單元的選擇性地輸出到數學邏輯單元。

該發明所涉及的微控制器的指令長度定義利用三個指令定義區域,其中用同一指令定義區域來規定立即數、運算元地址或目標地址,用另一指令定義區域來規定不同操作運算的操作碼,以及用還有一個指令定義區域來規定用於識別指令中的運算元地址或位置及目標地址或位置從而控制精簡指令集流水線結構中流水線各階段之間的數據傳遞的識別控制碼。

例如,一種指令長度為17位,其中把指令中的三位作為識別指令中的運算元地址或位置及目標地址或位置從而控制所述精簡指令集流水線結構中流水線各階段之間的數據傳遞的識別控制碼;把該指令中的八位作為指令所執行的立即數、運算元地址或目標地址;以及把該指令中的六位作為規定不同操作運算的操作碼。

例如,對於數學邏輯或循環移位運算,指令中的最低8位(第0位到第7位)表示立即數、運算元地址或目標地址;第8位到第13位表示操作碼;第14位到第16位用來識別指令中運算元位置及目標位置。當第16位為‘1’時,表示有一個運算元從累加器中讀出;當第16位為‘0’時,表示無運算元來自累加器。當第15位為‘1’時,表示有一個運算元從RAM中讀取,當第15位為‘0’時,表示無運算元從RAM中讀取。當第14位為‘1’時,表示目標是在RAM單元中,當第14位為‘0’時,表示寫結果的目標是累加器。

技術方案

《中央處理器或微控制器的數據相關判別及選擇傳遞電路》的技術方案可用圖2來說明。參考圖2,數據相關判別電路的各路輸入信號分別為處於RD階段的指令的最高三位(第14位到第16位)[圖2中的n1(或i16)、n5(或i15)和n3(或i14)],最低8位(第0位到第7位)[即圖2中的n7或i(7:0)],時鐘信號n4(或clk)及控制信號n2(或e_alu)、n6(或w_alu)。信號e_alu、w_alu分別代表EX階段及WR階段指令的操作類別。例如,當e_alu或w_alu為‘1’時,表示相應指令執行的是數學、邏輯或循環移位操作;否則,表示相應指令執行的是其它操作(如跳轉控制等)。

信號i14經暫存器REG1,延時一個時鐘周期後輸出信號n9及其反向信號n8;n9經暫存器REG3再延遲一個時鐘周期後輸出n15及反向信號n14。在數據選擇傳遞電路209中,輸入信號n19到n23分別為5個不同階段、不同來源的數據;n19為寫結果階段的運算結果w_result;n20為執行階段的運算結果e_result;n21為來自RAM的數據;n22為來自累加器的數據;n23為立即數。

根據前面關於i14、i15、i16的定義及流水線結構微控制器工作原理的敘述並結合圖2,可以知道,當n8=‘1’時,表示EX階段的寫結果目標為累加器,當n14=‘1’時,表示WR階段的寫結果目標為累加器。當n1、n2、n8同時都等於‘1’時,則與門AND1的輸出n12=‘1’;這表明RD階段指令的來自累加器的運算元是EX階段指令的運算結果,故必須將此運算結果提前傳遞給ALU211的A口,否則將得出錯誤的結果。n12連線到多路選擇器(MUX)1的控制端。因此時n12=‘1’,故EX階段的運算結果n20(e_result)被傳送到MUX1的輸出端n24。因為n12=‘1’時,n25也等於‘1’,故e_result進而被傳送到MUX5的輸出端n27。而n27將被傳送到ALU211的A口。同理,當n1、n6、n14同時為‘1’時,AND3的輸出n18=‘1’,這表示RD階段指令的來自累加器的運算元是WR階段指令的運算結果。此時,如果n12=‘0’,則WR階段指令的運算結果n19(w_result)將被傳送到ALU211的A口。如果n12、n18同時等於‘1’,那么只有e_result被傳送到ALU211的A口。這從圖2所示的電路是很容易看出的。

繼續參考圖2,RD階段指令中的地址n7(這裡及以下所說的地址可以是運算元的地址,也可以是目標地址),與EX階段指令中的地址n11輸入到地址比較器COM1。此時,如果n2(即e_alu)為‘1’,則COM1將對上述兩個地址進行比較,如果這兩個地址相同,則比較器的輸出n10=‘1’,否則n10=‘0’。

當n9=‘1’時,表示EX階段指令的寫結果目標為某一RAM單元。與此類似,當n15=‘1’時,表示W階段指令的寫結果目標為某一RAM單元。當n9、n5、n10同時都為‘1’時,則n13=‘1’,這表明RD階段指令中的來自RAM單元的運算元是EX階段指令的運算結果。故必須將此結果提前傳送到ALU211的B口,否則,將會產生“數據災難”(DataHazard),從而得到錯誤的結果。

當n13=‘1’時,MUX3將e_result傳送到輸出端n30。因此時也等於‘1’,MUX6選擇n30,故e_result進而被送到其輸出端n32並被送到ALU211的B口。同理,如果n15、n5、n16同時等於‘1’,則n28=‘1’,這表明RD階段指令中的來自RAM單元的運算元是WR階段指令中的運算結果。此時,如果n13=‘0’,則w_result將被傳送到ALU211的B口。如果n13、n28同時等於‘1’,那么只有e_result被傳送到ALU211的A口。

參考圖3來說明在精簡指令集流水線結構微控制器中套用該發明的實現方式。

(1)取指令階段(時鐘周期0):程式計數器201根據控制單元204輸出的控制信號Q3,輸出指令地址Q1。指令存儲器202根據地址Q1輸出對應的指令向量Q2(指令長度為17位)。

(2)讀運算元階段(時鐘周期1):指令向量Q2經指令暫存器203延時一個時鐘周期後通過該指令暫存器的輸出端203a傳送給指令解碼器205。該指令解碼器205將輸入的指令向量解碼後輸出各種不同的微代碼向量Q7、Q9、Q10、Q11。數據相關判別電路208根據來自指令解碼器205的各種微代碼向量,來判別在指令流水線中各階段的數據的相關性,並據此輸出數據選擇傳遞控制代碼向量Q15。數據選擇傳遞電路209,根據控制代碼向量Q15,從下列5個不同階段、不同來源的數據中選出2個適當的數據並分別傳遞給數學邏輯單元(ALU)211的A口與B口:

a.數學邏輯單元211在其輸出端211a處的運算結果輸出;

b.累加器212的輸出Q13;

b.寫結果暫存器206在輸出端206a處的輸出:

d.隨機存取存儲器207的數據輸出Q14;

e.指令解碼器205的輸出向量Q9(立即數)。

(3)執行階段:ALU211根據操作控制碼向量Q18對輸入運算元Q16、Q17進行相應的運算,並從其輸出端211a把運算結果輸送給寫結果暫存器206。

(4)寫結果階段:將存在寫結果暫存器206中的運算結果通過其輸出端206a寫入隨機存取存儲器207或累加器212中。

改善效果

《中央處理器或微控制器的數據相關判別及選擇傳遞電路》與專利背景中技術相比所具有的有益效果在於具有下列優點:電路更加簡單,因而更加可靠;採用該發明的精簡指令集流水線結構微控制器的晶片面積將相應縮小,因而成本也將隨之降低。

附圖說明

圖1是說明1999年12月前已有技術的精簡指令集流水線結構微控制器的工作原理的圖。

圖2是依據《中央處理器或微控制器的數據相關判別及選擇傳遞電路》的一個實施例的流水線結構微控制器的數據相關判別及選擇傳遞電路的方框圖。

圖3是說明使用依據該發明的精簡指令集流水線結構微控制器的工作原理圖。

權利要求

1.一種精簡指令集流水線結構的微控制器,其中所述微控制器包括一數據相關判別電路和一數據選擇傳遞電路,其特徵在於所述數據相關判別電路包括第一和第二地址比較器(COM1,COM2),所述第一地址比較器用於把所述微控制器的讀運算元階段的指令中的運算元地址與寫結果階段的指令中的目標地址進行比較,所述第二地址比較器用於把所述微控制器的執行階段的指令中的運算元地址與寫結果階段的指令中的運算元地址進行比較,所述數據選擇傳遞電路用於根據所述數據相關判別電路的比較結果把來自所述微控制器中的累加器、隨機存取存儲器、指令解碼器、寫結果暫存器和數學邏輯單元的信號選擇性地輸出到數學邏輯單元。

2.如權利要求1所述的精簡指令集流水線結構的微控制器,其特徵在於所述微控制器使用一種利用三個指令定義區域的指令,其中一指令定義區域為立即數、運算元地址或目標地址,另一指令定義區域為不同操作運算的操作碼,還有一個指令定義區域為用於識別指令中的運算元地址或位置及目標地址或位置從而控制精簡指令集流水線結構中流水線各階段之間的數據傳遞的識別控制碼。

3.如權利要求1所述的精簡指令集流水線結構的微控制器,其特徵在於所述三個指令定義區域總共為十七位,包括:作為識別指令中運算元地址或位置及目標地址或位置從而控制所述精簡指令集流水線結構中流水線各階段之間的數據傳遞的識別控制碼的三位;規定不同操作運算的操作碼的六位;以及作為為指令所執行的立即數、運算元地址或目標地址的八位。

4.如權利要求3所述的精簡指令集流水線結構的微控制器,其特徵在於所述三位為所述指令的最高三位,所述六位為所述指令的次高六位,所述八位為所述指令的最低八位。

5.如權利要求4所述的精簡指令集流水線結構的微控制器,其特徵在於所述三位的值分別表示是否有一運算元來自所述累加器、是否有一運算元來自所述RAM以及寫結果的目標是所述累加器還是所述RAM。

6.如權利要求5所述的精簡指令集流水線結構的微控制器,其特徵在於所述三位中的最高位表示是否有一運算元來自累加器,所述三位中的次高位表示是否有一運算元來自RAM,所述三位中的最低位表示寫結果的目標是累加器還是RAM。

7.如權利要求6所述的精簡指令集流水線結構的微控制器,其特徵在於如果所述三位中的最高位為‘1’,則表示有一運算元來自累加器,如果為‘0’,則表示沒有運算元來自累加器;如果所述三位中的次高位為‘1’,表示有一運算元來自RAM,如果為‘0’,則表示沒有運算元來自RAM;如果所述三位中的最低位為‘1’,則表示寫結果的目標是RAM,如果為‘0’,則表示寫結果的目標為累加器。

8.如權利要求6所述的精簡指令集流水線結構的微控制器,其特徵在於如果所述三位中的最高位為‘0’,則表示有一運算元來自累加器,如果為‘1’,則表示沒有運算元來自累加器;如果所述三位中的次高位為‘0’,表示有一運算元來自RAM,如果為‘1’,則表示沒有運算元來自RAM;如果所述三位中的最低位為‘0’,則表示寫結果的目標是RAM,如果為‘1’,則表示寫結果的目標為累加器。

9.如權利要求6到8中任一項所述的精簡指令集流水線結構的微控制器,其特徵在於所述數據相關判別電路包括第一到第四暫存器(REG1,REG2,REG3,REG4)、第一和第二比較器(COM1,COM2)、第一到第四與門(AND1,AND2,所述數據選擇傳遞電路包括第一到第六多路選擇器(MUX1,MUX2,MUX3,MUX4,MUX5,MUX6)及第一和第二或門(11,18)。

所述數據相關判別電路和數據選擇傳遞電路的特徵包括如下連線關係:第一與門的輸出,連線到第三與門的輸入;第一暫存器的反向輸出,連線到第一與門的輸入;第一暫存器的輸出,連線到第三暫存的輸入;第三暫存器的反相輸出,連線到第三與門的的輸入;第一與門和第三與門的輸出;連線到第一或門的輸入;第一與門的輸出,連線到MUX1的控制端;MUX1的輸入,分別連線來自寫結果階段和執行階段的輸入數據;MUX2的輸入,連線來自累加器和RAM的輸入數據:MUX5的輸入,連線MUX1和MUX2的輸出,輸出,連線到ALU的A口;第一地址比較器的輸入A,連線來自指令解碼的地址信號,輸入B,連線第二暫存器的輸出;第二暫存的輸出,連線第四暫存器的輸入;第二地址比較器的輸入B,連線第四暫存的輸出,輸入A,連線連線來自指令解碼的地址信號。第一地址比較器的輸出,連線第二與門的輸入;第二地址比較器的輸出,連線第四與門的輸入;第二或門的輸入,連線第二和第四與門的輸出。MUX3的控制端,連線第二與門的輸出,輸入端,分別連線來自執行階段和寫結果階段的數據:MUX4的輸入,分別連線來自RAM的讀運算元和解碼器的立即數:MUX6的控制端,連線來第二或門的輸出,輸入端,連線來自MUX3和MUX4的輸出,輸出端,連線ALU的B口。

實施方式

例一 考慮下列2條指令:

ADD A,X

SUB [m1],A

第一條指令所執行的運算是將立即數X與累加器A中的數據相加,並將結果存於A中。第二條指令所執行的操作是以m1為地址的RAM單元中的數據與累加器A中的數據相減,並將結果存於以m1為地址的RAM單元中。在此實例中,由於第2條指令中的運算元(即累加器中的數據)是第一條指令的運算結果,所以這兩條指令之間存在著數據相關性。於是,當第二條指令處於讀運算元階段時,數據相關判別電208將據此而輸出一個相應的數據選擇控制代碼Q15,此代碼驅使數據選擇傳遞電路209將其輸出端211a處第一條指令的運算結果作為Q16直接前遞(forwarding)給數學邏輯單元211的A口。

例二 考慮下列三條指令:

ADD [m1],A

INC [m2]

SUB A,[m2]

第一條指令執行的是以m1為地址的RAM單元中的數據與累加器中的數據相加並將結果存在以m1為地址的RAM單元中。第二條指令執行的是以m2為地址的RAM單元中的數據加1並將結果存在以m2為地址的RAM單元中。第三條指令所執行的是累加器中的數據與以m1為地址的RAM單元中的數據相減,並將結果存在累加器中。在此實例中,第一條指令與第二條指令無數據相關性,第二條指令與第三條指令也無數據相關性。但第一條指令與第三條指令存在著數據相關性。第三條指令的運算元[m1](即以m1為地址的RAM單元中的數據)是第一條指令的運算結果。當第三條指令處於讀運算元階段時,第一條指令處於寫結果階段,但此時其運算結果尚未寫入以m1為地址的RAM單元中。於是,在第一條指令處於讀運算元階段時,數據相關判別電路208輸出一個相應的數據選擇控制代碼Q15,此代碼驅使數據選擇傳遞電路209將其輸出端206a處第一條指令的運算結果作為Q17傳送到ALU211的B口。

榮譽表彰

2007年,《中央處理器或微控制器的數據相關判別及選擇傳遞電路》獲得第五屆江蘇省專利項目獎優秀獎。