專利背景

緊耦合共享存儲器體系結構有多種實現方法。常見的有

對稱多處理機(SMP)結構和非一致性存儲器訪問(NUMA)結構。如果

存儲器在物理上集中放置,任意處理器訪問集中存儲器的延遲都相等,則稱為對稱

多處理機。截至2008年1月,大多數2~4路Intel Xeon和Itanium系統都是通過共享系統匯流排方式實現的SMP。但是由於匯流排驅動能力和存儲器頻寬的限制,SMP系統規模難以做大,一般只限於2~8路。採用NUMA結構的計算機系統,其存儲器在物理上分布,處理器訪問本地存儲器延遲小,而訪問遠地存儲器延遲大。其互連方式通常採用兩級互連,第一級通過共享匯流排或點到點直連方式連線2~4個CPU,連同結點控制器構成一個處理器子系統,而處理器子系統間則使用定製或通用互連網路,構成更大的系統。

對於構建構建大規模多處理器系統,通常需要採用非一致性存儲器訪問(NUMA)結構。在這一體系結構的設計中,作為互連網路的核心交叉開關路由晶片NR,由於技術和工藝等問題,連線埠數目的增加具有一定的限制(截至2008年最大可做到16連線埠)。另~方面,由於結點控制器NC在物理空間上距離處理器較近,而距離互連網路(路由晶片NR)較遠,因而對於單個鏈路,兩側實際頻寬會出現不匹配的問題,即單鏈路處理器端實際頻寬要高於互連網路端實際頻寬。

在這種前提下,如果系統內處理器規模增加一倍,可以採用如下兩種方法。一種方法是:每個結點控制器NC通過n條鏈路連線處理器,通過另n條鏈路與交叉開關路由晶片相連線,由此為基礎構建兩倍處理器規模的緊耦合共享存儲器體系結構。由於單鏈路處理器端實際頻寬要高於互連網路端實際頻寬,因而結點控制器NC兩側的處理器頻寬與網路頻寬會出現不匹配的情況,即這種方法是以犧牲處理器頻寬與網路頻寬不匹配為代價,來獲取較低的網路通信延遲。

另一種方法是:每個結點控制器NC通過m條鏈路連線處理器,通過另n條鏈路與交叉開關路由晶片相連線,為保持處理器頻寬與網路頻寬基本匹配,需要m<n;但由此會明顯增加結點控制器NC的數量,由於交叉開關路由晶片NR最大連線埠數有限(截至2008年為16個),因而需要通過級聯交叉開關路由晶片NR構建提供更多連線埠數量的互連網路才可以,從而會增加網路互連跳步,即這種發發是以犧牲網路通信延遲為代價,來獲得處理器頻寬與網路頻寬的相對平衡。

當處理器規模擴展時,採用上述方法構建多處理器緊耦合共享存儲器結構,總會帶來或者處理器頻寬與網路頻寬不匹配,或者增加網路平均延遲的問題,似乎頻寬匹配和互連單跳步兩者不能兼得。那么能否有其他的方法,當處理器規模增加時,即要保持處理器頻寬與網路頻寬相匹配,又能最大限度減少互連網路平均延遲。這正是計算機領域科技人員要解決的問題。

發明內容

專利目的

《一種雙翼可擴展多處理器緊耦合共享存儲器體系結構》的目的是提供一種當處理器規模增加時,即能保持處理器頻寬與網路頻寬相匹配,又能減少互連網路平均延遲的一種共享存儲器體系結構。

技術方案

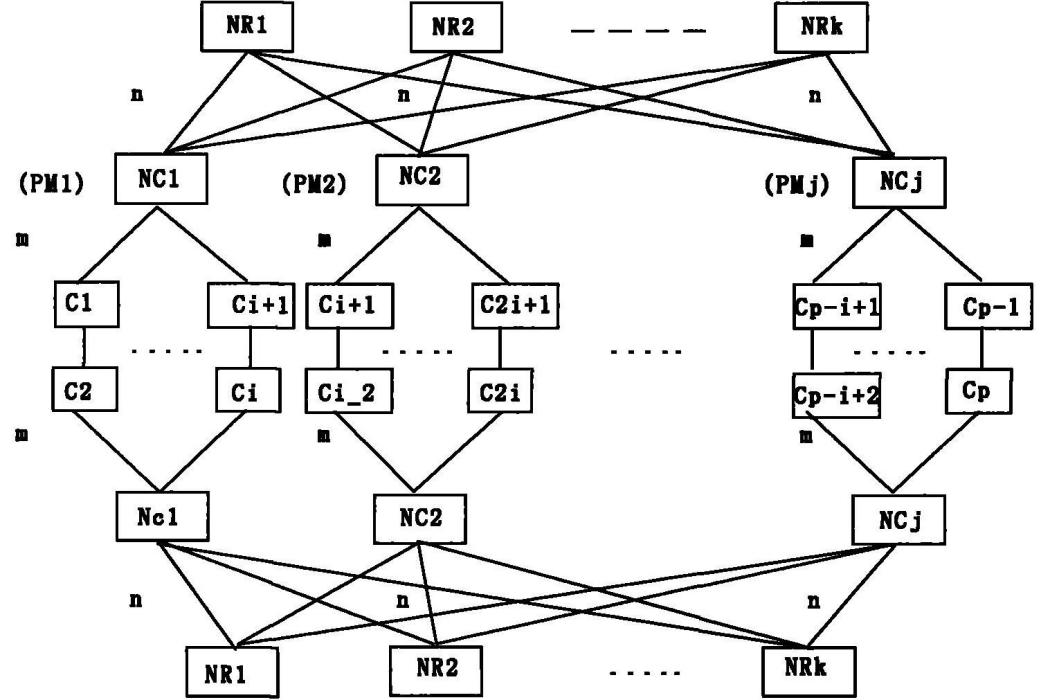

《一種雙翼可擴展多處理器緊耦合共享存儲器體系結構》在一個有p個處理器組成的緊耦合共享存儲器體系結構內,設定j個處理器模組PM,其中每個處理器模組PM由i個處理器C耦合交叉連線而成,且每處理器C只有一條鏈路與結點控制器NC直接連線;每個處理器模組PM還包含2個成對結點控制器NC,每個結點控制器NC通過m條鏈路與處理器連線,並通過n條鏈路與互連網路連線;互連網路共有兩組,每組互連網路連線k個q連線埠的交叉開關路由晶片NR,構成雙翼可擴展多處理器緊耦合共享存儲器體系結構。

體系結構內處理器數量是p=i*j,為實現處理器之間通信的無阻塞性,則需要i=2m,即m=i/2,同時為實現網路傳輸的無阻塞性,則需要n*j=q*k。假定處理器單鏈路頻寬為a,網路單鏈路頻寬為b,由於結點控制器NC距離處理器端較近,通常實際頻寬a>b,因而為保持處理器頻寬與網路頻寬的相對平衡,即am=bn,則要求m<n。在保持系統規模高可擴展的前提下,實現處理器頻寬與網路頻寬相對平衡,並同時保持較低的互連網路平均延遲。

處理器頻寬與網路頻寬的平衡,具體是指:當處理器規模增加一倍時,如果採用單個結點控制器NC通過n條鏈路連線處理器C,通過另n條鏈路連線交叉開關路由晶片NR的方式構建的緊耦合共享存儲器體系結構的雙翼可擴展多處理器p,雖然網路通信平均延遲較低,但處理器頻寬與網路頻寬的不匹配會嚴重影響系統性能。與這種方式相比,該系統結構具有更好的處理器頻寬與網路頻寬相對平衡的特性。

較低的互連網路平均延遲,具體是指:當處理器規模增加一倍時,如果採用單個結點控制器NC通過m條鏈路連線處理器C,通過另n條m<n鏈路連線交叉開關路由晶片NR構建p處理器緊耦合共享存儲器體系結構,雖然處理器頻寬與網路頻寬相對平衡,但必須通過級聯交叉開關路由晶片NR構建提供更多連線埠數量的互連網路,從而增加網際網路平均延遲。與這種方式相比,該發明的方法和體系結構具有較低的互連網路平均延遲。

有益效果

《一種雙翼可擴展多處理器緊耦合共享存儲器體系結構》通過m條鏈路連線處理器C,通過另n條鏈路與交叉開關路由晶片NR相連線,其中m<n,同時通過兩翼的兩套互連網路來構建p個處理器緊耦合共享存儲器體系結構,在保持系統規模高可擴展的前提下,實現處理器頻寬與網路頻寬相對平衡,同時保持較低的互連網路平均延遲。在保留2008年1月以前技術優點的同時,又能有效降低存在的負面問題。

附圖說明

圖1是雙翼可擴展多處理器緊耦合共享存儲器體系結構示意圖;

圖2是雙翼可擴展64處理器緊耦合共享存儲器體系結構示意圖;

圖3是傳統技術的一種構建64處理器緊耦合共享存儲器體系結構的拓撲結構示意圖;

圖4是傳統技術的另一種構建64處理器緊耦合共享存儲器體系結構的拓撲結構示意圖。

權利要求

1.雙翼可擴展多處理器緊耦合共享存儲器體系結構的構建方法,其特徵在於在一個雙翼可擴展的有p個處理器緊耦合共享存儲器體系結構內,包含j個處理器模組PM,其中每個處理器模組PM由i個處理器C耦合交叉連線而成,且每處理器C只有一條鏈路與結點控制器NC直接連線;每個處理器模組PM包含2個成對結點控制器NC,每個結點控制器NC通過m條鏈路與處理器C連線,並通過n條鏈路與互連網路連線;互連網路共有兩組,每組互連網路連線k個q連線埠交叉開關路由晶片NR,其中:

處理器C的數量是p=i×j,為實現處理器之間通信的無阻塞性,則需要i=2m,即m=i/2,同時為實現網路傳輸的無阻塞性,則需要n×j=q×k,假定處理器單鏈路頻寬為a,網路單鏈路頻寬為b,由於結點控制器NC距離處理器C端較近,實際頻寬a>b,為保持處理器C頻寬與網路頻寬的相對平衡,即am=bn,則要求m<n。

實施方式

如附圖2所示構建64路處理器為例,闡述雙翼可擴展多處理器緊耦合共享存儲器體系結構的具體實現方式。

在一個64處理器規模的緊耦合共享存儲器體系結構內,即p=16,在每個處理器模組由4個處理器C耦合交叉連線而成,即i=4,由於p=i*j,因而系統內處理器模組(PM)的數量j=p/i=16。

每個處理器模組PM包含2個成對結點控制器NC,每個結點控制器NC通過m條鏈路與處理器C連線,為實現處理器之間通信的無阻塞性,則需要i=2m,即m=i/2=2,即單個結點控制器NC通過2條鏈路與處理器連線。

假定處理器單鏈路頻寬為a,網路單鏈路頻寬為b,由於結點控制器NC距離處理器端較近,通常實際頻寬a>b,因而為保持處理器頻寬與網路頻寬的相對平衡,即am=bn,則要求m<n。以

截至2008年1月,技術實現的單鏈路處理器頻寬和單鏈路網路通信頻寬分別為25.6GB/s和15GB/s為例,n=am/b=25.5*2/15=3.4,滿足條件的最小n整數值為4,即n=4。

每個結點控制器NC還通過n條鏈路與互連網路連線,互連網路共有兩組,每組互連網路由k個q連線埠交叉開關路由晶片NR組成。為實現網路傳輸的無阻塞性,則需要n*j=q*k,由於技術上和工藝上的限制,2008年1月以前交叉開關路由晶片NR連線埠數最大只能做到16連線埠,即q=16,因而單翼互連網路內部交叉開關路由晶片NR數量k=n*j/q=4*16/16=4,即單翼互連網路包含4個交叉開關路由晶片NR。通過上述連線方式,構成雙翼可擴展64處理器緊耦合共享存儲器體系結構。

下面通過描述方法一與方法二的構建方式,通過對比分析,來闡述該發明體系結構的優異特性。

當由32處理器系統擴展到64處理器系統時,在交叉開關路由晶片NR連線埠數為16的前提下,通常會通過以下兩種方式實現:

一種方法如圖3所示,採用單個結點控制器NC通過4條鏈路連線處理器C,通過另4條鏈路連線交叉開關路由晶片NR,即m=n=4,考慮到網路傳輸的無阻塞性,則需要n*j=q*k,k=n*j/q=4*16/16=4,即互連網路內部交叉開關路由晶片NR數量為4。同時,單個結點控制器NC一側的處理器頻寬am=25.5GB/s*4=102GB/s,另一側的網路頻寬bn=15GB/s*4=60GB/s,從而帶來處理器頻寬與網路頻寬嚴重不匹配的問題。因而採用這種方式,是以犧牲處理器頻寬與網路頻寬不匹配為代價,來獲取較低的網路通信延遲的。

另一種方法是如圖4所示,在每個處理器模組內部,由2個處理器C通過QPI通道耦合交叉連線而成,即i=2,由於p=i*j,因而系統內處理器模組PM的數量j=p/i=32。

每個處理器模組PM包含1個結點控制器NC,單個結點控制器NC通過m條鏈路與處理器連線,為實現處理器之間通信的無阻塞性,則需要m=i=2,即單個結點控制器NC通過2條鏈路與處理器連線。同時,為保持處理器頻寬與網路頻寬的相對平衡,即am=bn,則要求m<n。這裡m=2,a=25.6GB/s,b=15GB/s,從而滿足條件的最小n整數值為4,即n=4。考慮到網路傳輸的無阻塞性,則需要n*j=q*k=4*32=128,即互連網路需要提供128個通信鏈路,因而無法通過一級16連線埠交叉開關路由晶片NR實現,只能通過二級級聯方式構建128連線埠數量的互連網路,從而提高了互連網路通信平均延遲。綜上,採用這種方式,是以犧牲網路通信平均延遲為代價,來獲得處理器頻寬與網路頻寬的相對平衡的。

與上述兩種方法相比,《一種雙翼可擴展多處理器緊耦合共享存儲器體系結構》的體系結構的優勢在於:在保持系統從32處理器規模到64處理器規模可擴展的前提下,實現了處理器頻寬與網路頻寬相對平衡,同時保持較低的互連網路平均延遲。即在保持方法一中處理器頻寬與網路頻寬相對平衡的特性基礎上,互連網路平均延遲與方法二相比約降低50%左右。

榮譽表彰

2013年10月,《一種雙翼可擴展多處理器緊耦合共享存儲器體系結構》獲得第十五屆中國專利優秀獎。