PCI定義

PCI匯流排特點

PCI 匯流排結構圖

PCI即Peripheral Component Interconnect,中文意思是“外圍器件互聯”,是由PCISIG (PCI Special Interest Group)推出的一種局部並行匯流排標準。PCI匯流排是由ISA(Industy Standard Architecture)匯流排發展而來的,ISA並行匯流排有8位和16位兩種模式,時鐘頻率為8MHz,工作頻率為33MHz/66MHz。是一種同步的獨立於處理器的32位或64位局部匯流排。從結構上看,PCI是在CPU的供應商和原來的系統匯流排之間插入的一級匯流排,具體由一個橋接電路實現對這一層的管理,並實現上下之間的接口以協調數據的傳送。從1992年創立規範到如今,PCI匯流排已成為了計算機的一種標準匯流排。已成為局部匯流排的新標準,廣泛用於當前高檔微機、工作站,以及攜帶型微機。主要用於連線顯示卡、網卡、音效卡。PCI匯流排是32位同步復用匯流排。其地址和數據線引腳是AD31~AD0。PCI的工作頻率為33MHz。

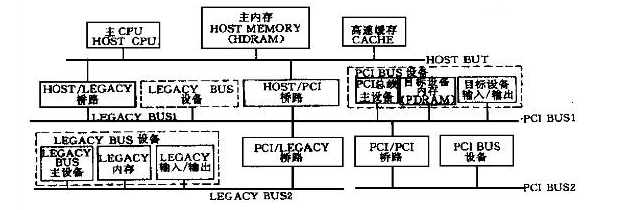

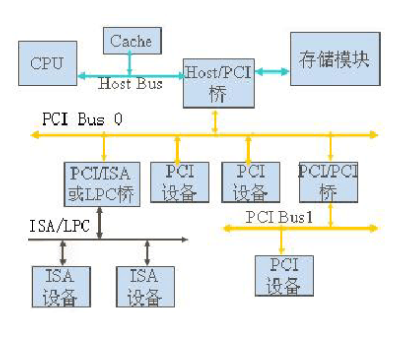

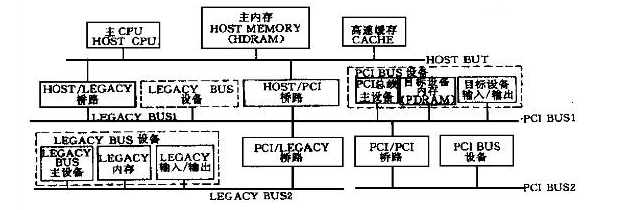

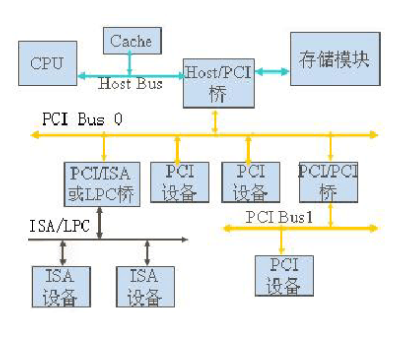

PCI匯流排結構

PCI匯流排是一種樹型結構,並且獨立於CPU匯流排,可以和CPU匯流排並行操作。PCI匯流排上可以掛接PCI設備和PCI橋片,PCI匯流排上只允許有一個PCI主設備,其他的均為PCI 從設備,而且讀寫操作只能在主從設備之間進行,從設備之間的數據交換需要通過主設備中轉。PCI匯流排結構如下圖所示。

在處理器系統中,含有PCI匯流排和PCI匯流排樹這兩個概念。這兩個概念並不相同,在一顆PCI匯流排樹中可能具有多條PCI匯流排,而具有血緣關係的PCI匯流排組成一顆PCI匯流排樹。PCI匯流排由HOST主橋或者PCI橋管理,用來連線各類設備,如音效卡、網卡和IDE接口卡等。在一個處理器系統中,可以通過PCI橋擴展PCI匯流排,並形成具有血緣關係的多級PCI匯流排,從而形成PCI匯流排樹型結構。在處理器系統中有幾個HOST主橋,就有幾顆這樣的PCI匯流排樹,而每一顆PCI匯流排樹都與一個PCI匯流排域對應。

與HOST主橋直接連線的PCI匯流排通常被命名為PCI匯流排0。考慮到在一個處理器系統中可能有多個主橋。

PCI匯流排取代了早先的

ISA匯流排。當然與在PCI匯流排後面出現專門用於顯示卡的AGP匯流排,與現在的PCI Express匯流排相比,功能沒有那么強大,但是PCI能從1992用到現在,說明他有許多優點,比如即插即用(Plug and Play)、中斷共享等。在這裡我們對PCI匯流排做一個深入的介紹。

從數據寬度上看,PCI匯流排有32bit、64bit之分;從匯流排速度上分,有33MHz、66MHz兩種。目前流行的是32bit @ 33MHz,而64bit系統正在普及中。改良的PCI系統,

PCI-X,最高可以達到64bit @ 133MHz,這樣就可以得到超過1GB/s的

數據傳輸速率。如果沒有特殊說明,以下的討論以32bit @ 33MHz為例。

不同於ISA匯流排,PCI匯流排的

地址匯流排與

數據匯流排是

分時復用的。這樣做的好處是,一方面可以節省接外掛程式的管腳數,另一方面便於實現突發數據傳輸。在做數據傳輸時,由一個PCI設備做發起者(主控,Initiator或Master),而另一個PCI設備做目標(從設備,Target或Slave)。匯流排上的所有時序的產生與控制,都由Master來發起。PCI匯流排在同一時刻只能供一對設備完成傳輸,這就要求有一個仲裁機構(Arbiter),來決定在誰有權力拿到匯流排的主控權。

當PCI匯流排進行操作時,發起者(Master)先置REQ#,當得到仲裁器(Arbiter)的許可時(GNT#),會將FRAME#置低,並在AD匯流排上放置Slave地址,同時C/BE#放置命令信號,說明接下來的傳輸類型。所有PCI匯流排上設備都需對此地址解碼,被選中的設備要置DEVSEL#以聲明自己被選中。然後當IRDY#與TRDY#都置低時,可以傳輸數據。當Master數據傳輸結束前,將FRAME#置高以標明只剩最後一組數據要傳輸,並在傳完數據後放開IRDY#以釋放匯流排控制權。

這裡我們可以看出,PCI匯流排的傳輸是很高效的,發出一組地址後,理想狀態下可以連續發數據,峰值速率為132MB/s。實際上,目前流行的33M@32bit北橋晶片一般可以做到100MB/s的連續傳輸。

PCI匯流排特點

(1)傳輸速率高最大數據傳輸率為132MB/s,當數據寬度升級到64位,數據傳輸率可達264MB/s。這是其他匯流排難以比擬的。它大大緩解了數據I/O瓶頸,使高性能CPU的功能得以充分發揮,適應高速設備數據傳輸的需要。

(2)多匯流排共存採用PCI匯流排可在一個系統中讓多種匯流排共存,容納不同速度的設備一起工作。通過HOST-PCI橋接組件晶片,使CPU匯流排和PCI匯流排橋接;通過PCI-ISA/EISA橋接組件晶片,將PCI匯流排與ISA/EISA匯流排橋接,構成一個分層次的多匯流排系統。高速設備從ISA/EISA匯流排卸下來,移到PCI匯流排上,低速設備仍可掛在ISA/EISA匯流排上,繼承原有資源,擴大了系統的兼容性。

(3)獨立於CPU PCI匯流排不依附於某一具體處理器,即PCI匯流排支持多種處理器及將來發展的新處理器,在更改處理器品種時,更換相應的橋接組件即可。

(4)自動識別與配置外設 用戶使用方便。

(5)並行操作能力。

PCI匯流排的主要性能

(1)匯流排時鐘頻率33.3MHz/66.6MHz。

(2)匯流排寬度32位/64位。

(3)最大數據傳輸率132MB/s(264MB/s)。

(4)支持64位定址。

(5)適應5V和3.3V電源環境。

即插即用的實現

所謂即插即用,是指當

板卡插入系統時,系統會自動對板卡所需資源進行分配,如基地址、

中斷號等,並自動尋找相應的驅動程式。而不象舊的ISA

板卡,需要進行複雜的手動配置。

實際的實現遠比說起來要複雜。在PCI板卡中,有一組暫存器,叫"配置空間"(Configuration Space),用來存放基地址與記憶體地址,以及中斷等信息。

以

記憶體地址為例。當上電時,

板卡從ROM里讀取固定的值放到暫存器中,對應記憶體的地方放置的是需要分配的記憶體位元組數等信息。

作業系統要跟據這個信息分配記憶體,並在分配成功後把相應的暫存器中填入記憶體的起始地址。這樣就不必手工設定開關來分配記憶體或基地址了。對於中斷的分配也與此類似。

中斷共享的實現

ISA卡的一個重要局限在於中斷是獨占的,而我們知道計算機的

中斷號只有16個,系統又用掉了一些,這樣當有多塊ISA卡要用中斷時就會有問題了。

硬體上,採用電平觸發的辦法:中斷信號在系統一側用電阻接高,而要產生中斷的

板卡上利用三極體的集電極將信號拉低。這樣不管有幾塊板產生中斷,中斷信號都是低;而只有當所有

板卡的中斷都得到處理後,中斷信號才會恢復高電平。

軟體上,採用中斷鏈的方法:假設系統啟動時,發現

板卡A用了中斷7,就會將中斷7對應的記憶體區指向A卡對應的

中斷服務程式入口ISR_A;然後系統發現板卡B也用中斷7,這時就會將中斷7對應的記憶體區指向ISR_B,同時將ISR_B的結束指向ISR_A。以此類推,就會形成一個中斷鏈。而當有中斷髮生時,系統跳轉到中斷7對應的記憶體,也就是ISR_B。ISR_B就要檢查是不是B卡的中斷,如果是,要處理,並將

板卡上的拉低電路放開;如果不是,則呼叫ISR_A。這樣就完成了中斷的共享。

通過以上討論,我們不難看出,PCI匯流排有著極大的的優勢。而近年來的市場情況也證實了這一點。

匯流排設備

在PCI匯流排中有三類設備,PCI主設備、PCI從設備和橋設備。其中PCI從設備只能被動地接收來自HOST主橋,或者其他PCI設備的讀寫請求;而PCI主設備可以通過匯流排仲裁獲得PCI匯流排的使用權,主動地向其他PCI設備或者主存儲器發起存儲器讀寫請求。而橋設備的主要作用是管理下游的PCI匯流排,並轉發上下游匯流排之間的匯流排事務。

一個PCI設備可以即是主設備也是從設備,但是在同一個時刻,這個PCI設備或者為主設備或者為從設備。PCI匯流排規範將PCI主從設備統稱為PCI Agent設備。在處理器系統中常見的PCI網卡、顯示卡、音效卡等設備都屬於PCI Agent設備。

在PCI匯流排中,HOST主橋是一個特殊的PCI設備,該設備可以獲取PCI匯流排的控制權訪問PCI設備,也可以被PCI設備訪問。但是HOST主橋並不是PCI設備。PCI規範也沒有規定如何設計HOST主橋。

在PCI匯流排中,還有一類特殊的設備,即橋設備。橋設備包括PCI橋、PCI-to-(E)ISA橋和PCI-to-Cardbus橋。PCI橋的存在使PCI匯流排極具擴展性,處理器系統可以使用PCI橋進一步擴展PCI匯流排。

PCI橋的出現使得採用PCI匯流排進行大規模系統互連成為可能。但是在目前已經實現的大規模處理器系統中,並沒有使用PCI匯流排進行處理器系統與處理器系統之間的大規模互連。因為PCI匯流排是一個以HOST主橋為根的樹型結構,使用主從架構,因而不易實現多處理器系統間的對等互連。

即便如此PCI橋仍然是PCI匯流排規範的精華所在,掌握PCI橋是深入理解PCI體系結構的基礎。PCI橋可以連線兩條PCI匯流排,上游PCI匯流排和下游PCI匯流排,這兩個PCI匯流排屬於同一個PCI匯流排域,使用PCI橋擴展的所有PCI匯流排都同屬於一個PCI匯流排域。

其中對PCI設備配置空間的訪問可以從上游匯流排轉發到下游匯流排,而數據傳送可以雙方向進行。在PCI匯流排中,還存在一種非透明PCI橋,該橋片不是PCI匯流排規範定義的標準橋片,但是適用於某些特殊套用。

主要性能

(1)傳輸速率高最大數據傳輸率為132MB/s,當數據寬度升級到64位,數據傳輸率可達264MB/s。這是其他匯流排難以比擬的。它大大緩解了數據I/O瓶頸,使高性能CPU的功能得以充分發揮,適應高速設備數據傳輸的需要。

(2)多匯流排共存採用PCI匯流排可在一個系統中讓多種匯流排共存,容納不同速度的設備一起工作。通過HOST-PCI橋接組件晶片,使CPU匯流排和PCI匯流排橋接;通過PCI-ISA/EISA橋接組件晶片,將PCI匯流排與ISA/EISA匯流排橋接,構成一個分層次的多匯流排系統。高速設備從ISA/EISA匯流排卸下來,移到PCI匯流排上,低速設備仍可掛在ISA/EISA匯流排上,繼承原有資源,擴大了系統的兼容性。

(3)獨立於CPU PCI匯流排不依附於某一具體處理器,即PCI匯流排支持多種處理器及將來發展的新處理器,在更改處理器品種時,更換相應的橋接組件即可。

(4)自動識別與配置外設 用戶使用方便。

(5)並行操作能力。

PCI (Peripheral Component Interconnect)匯流排是一種高性能

局部匯流排,是為了滿足外設間以及外設與主機間高速數據傳輸而提出來的。在數字圖形、圖像和

語音處理,以及高速實時

數據採集與處理等對

數據傳輸率要求較高的套用中,採用PCI匯流排來進行數據傳輸,可以解決原有的標準匯流排數據傳輸率低帶來的瓶頸問題。

匯流排特點

PCI匯流排是一種同步的獨立於處理器的32位或64位

局部匯流排,最高

工作頻率為33MHz,峰值速度在32位時為132MB/s,64位時為264MB/s,匯流排規範由PCISIG發布。ISA匯流排相比,PCI匯流排和有如下顯著的特點:

(1)高速性

PCI

局部匯流排以33MHz的

時鐘頻率操作,採用32位

數據匯流排,

數據傳輸速率可高達132MB/s,遠超過以往各種匯流排。而早在1995年6月推出的PCI匯流排規範2。l已定義了64位、66MHz的PCI

匯流排標準。因此PCI匯流排完全可為未來的計算機提供更高的

數據傳送率。另外,PCI匯流排的主設備(Master)可與微機記憶體直接交換數據,而不必經過微機CPU中轉,也提高了數據傳送的效率。

(2)即插即用性

目前隨著

計算機技術的發展,微機中留給用戶使用的硬體資源越來越少,也越來越含糊不清。在使用ISA板卡時,有兩個問題需要解決:一是在同一台微機上使用多個不同廠家、不同型號的板卡時,板卡之間可能會有硬體資源上的衝突;二是板卡所占用的硬體資源可能會與系統硬體資源(如音效卡、網卡等)相衝突。而PCI

板卡的硬體資源則是由微機根據其各自的要求統一分配,決不會有任何的衝突問題。因此,作為PCI

板卡的設計者,不必關心微機的哪些資源可用,哪些資源不可用,也不必關心板卡之間是否會有衝突。因此,即使不

考慮PCI匯流排的高速性,單憑其即插即用性,就比ISA匯流排優越了許多。

(3)可靠性

PCI獨立於處理器的結構,形成一種獨特的中間緩衝器設計方式,將

中央處理器子系統與外圍設備分開。這樣用戶可以隨意增添外圍設備,以擴充電腦系統而不必擔心在不同

時鐘頻率下會導致性能的下降。與原先微機常用的ISA匯流排相比,PCI匯流排增加了奇偶校驗錯(PERR)、系統錯(SERR)、從設備結束(STOP)等控制信號及逾時處理等可靠性措施,使數據傳輸的可靠性大為增加。

(4)複雜性

PCI匯流排強大的功能大大增加了硬體設計和

軟體開發的實現難度。硬體上要採用大容量、高速度的CPLD或FPGA晶片來實現PCI匯流排複雜的功能。

軟體上則要根據所用的

作業系統,用

軟體工具編制支持

即插即用功能酶設備

驅動程式。

(5)自動配置

PCI匯流排規範規定PCI插卡可以自動配置。PCI定義了3種

地址空間:

存儲器空間,輸入輸出空間和配置空間,每個PCI設備中都有256位元組的配置空間用來存放自動配置信息,當PCI插卡插入系統,BIOS將根據讀到的有關該卡的信息,結合系統的實際情況為插卡分配存儲地址、中斷和某些定時信息。

(6)共享中斷

PCI匯流排是採用低電平有效方式,多箇中斷可以共享一條中斷線,而ISA匯流排是邊沿觸發方式。

(7)擴展性好

如果需要把許多設備連線到PCI匯流排上,而匯流排驅動能力不足時,可以採用多級PCI匯流排,這些匯流排上均可以並發工作,每個匯流排上均可掛接若干設備。因此PCI

匯流排結構的擴展性是非常好的。由於PCI的設計是要輔助現有的擴展匯流排標準,因此與ISA,EISA及MCA匯流排完全兼容。

(8)多路復用

在PCI匯流排中為了最佳化設計採用了

地址線和數據線共用一組物理線路,即多路復用。PCI接外掛程式尺寸小,又採用了多路復用技術,減少了元件和管腳個數,提高了效率。

(9)嚴格規範

PCI匯流排對協定、時序、電氣性能、機械性能等指標都有嚴格的規定,保證了PCI的可靠性和兼容性。由於PCI匯流排規範十分複雜,其接口的實現就有較高的技術難度。

匯流排信號

PCI匯流排信號定義示意圖

PCI匯流排標準所定義的信號線通常分成必需的和可選的兩大類。其信號線總數為120條(包括電源、地、保留引腳等)。其中,必需信號線:主控設備49條,目標設備47條。可選信號線:51條(主要用於64位擴展、中斷請求、高速快取支持等)。主設備是指取得了匯流排控制權的設備,而被主設備選中以進行數據交換的設備稱為從設備或目標設備。作為主設備需要49條信號線,若作為目標設備,則需要47條信號線,可選的信號線有51條。利用這些信號線便可以傳輸數據、地址,實現接口控制、仲裁及系統的功能。PCI局部匯流排信號如下所示。下面按功能分組進行說明:

1)系統信號CLK IN:系統時鐘信號,為所有PCI傳輸提供時序,對於所有的PCI設備都是輸入信號。其頻率最高可達33MHz/66MHz,這一頻率也稱為PCI的工作頻率。 RST# IN:復位信號。用來迫使所有PCI專用的暫存器、定序器和信號轉為初始狀態。

2).地址和數據信號 AD[31::00]T/S:地址、數據復用的信號。PCI匯流排上地址和數據的傳輸,必需在FRAME#有效期間進行。當FRAME#有效時的第1個時鐘,AD[31::00]上的信號為地址信號,稱地址期;當IRDY#和TRDY#同時有效時,AD[31::00]上的信號為數據信號,稱數據期。一個PCI匯流排傳輸周期包含一個地址期和接著的一個或多個數據期。 C/BE[3::0]# T/S:匯流排命令和位元組允許復用信號。在地址期,這4條線上傳輸的時匯流排命令;在數據期,它們傳輸的時位元組允許信號,用來指定在數據期,AD[31::00]線上4個數據位元組中哪些位元組為有效數據,以進行傳輸。 PAR T/S:奇偶校驗信號。它通過AD[31::00]和C/BE[3::0]進行奇偶校驗。主設備為地址周期和寫數據周期驅動PAR,從設備為讀數據周期驅動PAR。

3).接口控制信號 FRAME# S/T/S:幀周期信號,由主設備驅動。表示一次匯流排傳輸的開始和持續時間。當FRAME#有效時,預示匯流排傳輸的開始;在其有效期間,先傳地址,後傳數據;當FRAME#撤消時,預示匯流排傳輸結束,並在IRDY#有效時進行最後一個數據期的數據傳送。 IRDY# S/T/S:主設備準備好信號。IRDY#要與TRDY#聯合使用,當二者同時有效時,數據方能傳輸,否則,即為未準備好二進入等待周期。在寫周期,該信號有效時,表示數據已由主設備提交到AD[31::00]線上;在讀周期,該信號有效時,表示主設備已做好接收數據的準備。 TRDY# S/T/S:從設備(被選中的設備)準備好信號。同樣TRDY#要與IRDY#聯合使用,只有二者同時有效,數據才能傳輸。 STOP# S/T/S:從設備要求主設備停止當前的數據傳送的信號。顯然,該信號應由從設備發出。LOCK# S/T/S:鎖定信號。當對一個設備進行可能需要多個匯流排傳輸周期才能完成的操作時,使用鎖定信號LOCK#,進行獨占性訪問。例如,某一設備帶有自己的存儲器,那么它必需能進行鎖定,以便實現對該存儲器的完全獨占性訪問。也就是說,對此設備的操作是排它性的。IDSEL IN:初始化設備選擇信號。在參數配置讀/寫傳輸期間,用作片選信號。 DEVSEL# S/T/S:設備選擇信號。該信號由從設備在識別處地址時發出,當它有效時,說明匯流排上有某處的某一設備已被選中,並作為當前訪問的從設備。

4).仲裁信號(只用於匯流排主控器) REQ# T/S:匯流排占用請求信號。該信號有效表明驅動它的設備要求使用匯流排。它是一個點到點的信號線,任何主設備都有它自己的REQ#信號。 GNT# T/S:匯流排占用允許信號。該信號有效,表示申請占用匯流排的設備的請求已獲得比準。

5).錯誤報告信號 PERR# S/T/S:數據奇偶校驗錯誤報告信號。一個設備只有在回響設備選擇信號(DEVSEL#)和完成數據期之後,才能報告一個PERR#。SERR# O/D:系統錯誤報告信號。用做報告地址奇偶錯、特殊命令序列中的數據奇偶錯,以及其他可能引起災難性後果的系統錯誤。它可由任何設備發出。

6).中斷信號 在PCI匯流排中,中斷是可選項,不一定必須具有。INTA# O/D:用於請求中斷。INTB# O/D、INTC# O/D、INTD# O/D:用於請求中斷,僅對多功能設備有意義。所謂的多功能設備是指:將幾個相互獨立的功能集中在一個設備中。各功能與中斷線之間的連線是任意的,沒有任何附加限制。

7.)其他可選信號 (1)高速快取支持信號:SBO# IN/OUT、SDONE IN/OUT (2)64位匯流排擴展信號:REQ64# S/T/S、ACK65# S/T/S、AD[63::32]T/S、C/BE[7::4]#T/S、PAR64 T/S。 (3)測試訪問連線埠/邊界掃描信號:TCK IN、TDI IN、TDO OUT、TMS IN、TRST# IN。