《CIS器件的深溝槽隔離形成方法、半導體器件結構》是華虹半導體(無錫)有限公司、上海華虹宏力半導體製造有限公司於2021年1月20日申請的專利,該專利公布號為CN112928058A,專利公布日為2021年6月8日,發明人是李佳龍、黃鵬、范曉、錢文生。

基本介紹

- 中文名:CIS器件的深溝槽隔離形成方法、半導體器件結構

- 申請公布號:CN112928058A

- 申請公布日:2021.06.08

- 申請號:202110075783X

- 申請日:2021.01.20

- 申請人:華虹半導體(無錫)有限公司; 上海華虹宏力半導體製造有限公司

- 地址:214028江蘇省無錫市新吳區新洲路30號

- 發明人:李佳龍; 黃鵬; 范曉; 錢文生

- Int. Cl.:H01L21/762(2006.01)I; H01L27/146(2006.01)I

- 專利代理機構:上海浦一智慧財產權代理有限公司31211

- 代理人:羅雅文

專利摘要

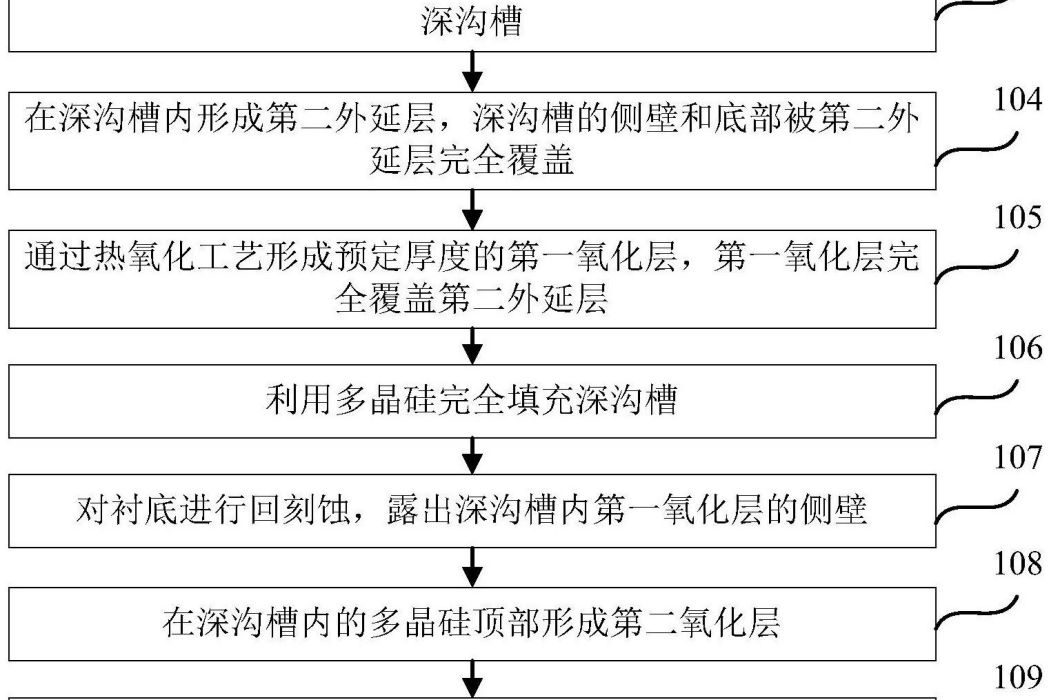

本申請公開了一種CIS器件的深溝槽隔離形成方法、半導體器件結構,涉及半導體製造領域。該方法包括在襯底上生長第一外延層;形成硬掩膜層;在第一外延層中形成若干個縱橫排列的深溝槽;在深溝槽內形成第二外延層;在深溝槽內第二外延層的表面形成第一氧化層;利用多晶矽完全填充深溝槽;對襯底進行回刻蝕,露出深溝槽內第一氧化層的側壁;在多晶矽頂部形成第二氧化層;去除硬掩膜層和第二氧化層上方的第一氧化層;快速生長第三外延層;對襯底表面進行CMP處理,在襯底上形成深溝槽隔離;解決了外延生長方式形成CIS器件的深溝槽隔離時,深溝槽交叉區域的頂部容易出現封口缺陷的問題;最佳化了深溝槽隔離的形成工藝,提升了器件性能。