發展起源

名字由來

1997年,由ATMEL公司挪威設計中心的A先生與V先生利用ATMEL公司的Flash新技術,共同研發出RISC精簡指令集的高速8位單片機,簡稱AVR。

功能特點

RISC 優先選取使用頻率最高的簡單指令,避免複雜指令:並固定指令寬度,減少指令格式和定址方式的種類,從而縮短指令周期,提高運行速度。由於 AVR 採用了 RISC 的這種結構,使AVR系列單片機都具備了1MIPS/MHz(百萬條指令每秒/兆赫茲)的高速處理能力。

早期單片機主要由於工藝及設計水平不高、功耗高和抗干擾性能差等原因,所以採取穩妥方案:即採用較高的分頻係數對時鐘分頻,使得指令周期長,執行速度慢。以後的CMOS單片機雖然採用提高時鐘頻率和縮小分頻係數等措施,但這種狀態並未被徹底改觀(51以及51兼容)。此間雖有某些精簡指令集單片機(RISC)問世,但依然沿襲對時鐘分頻的作法。

AVR單片機的推出,徹底打破這種舊設計格局,廢除了機器周期,拋棄複雜指令計算機(CISC)追求指令完備的做法;採用

精簡指令集,以字作為指令長度單位,將內容豐富的運算元與操作碼安排在一字之中(指令集中占大多數的單周期指令都是如此),取指周期短,又可預取指令,實現流水作業,故可高速執行指令。

當然這種速度上的升躍,是以高可靠性為其後盾的。AVR單片機硬體結構採取8位機與16位機的折中策略,即採用局部暫存器存堆(32個暫存器檔案)和單體高速輸入/輸出的方案(即輸入捕獲暫存器、輸出比較匹配暫存器及相應控制邏輯)。提高了指令執行速度(1Mips/MHz),克服了瓶頸現象,增強了功能;同時又減少了對外設管理的開銷,相對簡化了硬體結構,降低了成本。

故AVR單片機在軟/硬體開銷、速度、性能和成本諸多方面取得了最佳化平衡,是高性價比的單片機。

AVR單片機內嵌高質量的

Flash程式存儲器,擦寫方便,支持ISP和IAP,

便於產品的調試、開發、生產、更新。內嵌長壽命的

EEProm可長期保存關鍵數據,避免斷電丟失。片內大容量的RAM不僅能滿足一般場合的使用,同時也更有效的支持使用高級語言開發系統程式,並可像

MCS-51單片機那樣擴展外部

RAM。

AVR單片機的I/O線全部帶可設定的上拉電阻、可單獨設定為輸入/輸出、可設定(初始)高阻輸入、驅動能力強(可省去功率驅動器件)等特性,使的得I/O口資源靈活、功能強大、可充分利用。

AVR單片機片內具備多種獨立的時鐘分頻器,分別供URAT、I2C、SPI使用。其中與8/16位定時器配合的具有多達10位的預分頻器,可通過軟體設定分頻係數提供多種檔次的定時時間。

AVR單片機獨有的“以定時器/計數器(單)雙向計數形成三角波,再與輸出比較匹配暫存器配合,生成占空比可變、頻率可變、相位可變方波的設計方法(即脈寬調製輸出PWM)更是令人耳目一新。

增強性的高速同/異步串口,具有硬體產生校驗碼、硬體檢測和校驗偵錯、兩級接收緩衝、波特率自動調整定位(接收時)、禁止數據幀等功能,提高了通信的可靠性,方便程式編寫,更便於組成分散式網路和實現多機通信系統的複雜套用,串口功能大大超過MCS-51/96單片機的串口,加之AVR單片機高速,中斷服務時間短,故可實現高

波特率通訊。

面向位元組的高速硬體串列接口TWI、SPI。TWI與I2C接口

兼容,具備ACK信號硬體傳送與識別、地址識別、匯流排仲裁等功能,能實現主/從機的收/發全部4種組合的多機通信。SPI支持主/從機等4種組合的多機通信。

AVR單片機有自動上電

復位電路、獨立的看門狗電路、低電壓檢測電路BOD,多個復位源(自動上下電復位、外部復位、看門狗復位、BOD復位),可設定的啟動後延時運行程式,

增強了嵌入式系統的可靠性。AVR單片機具有多種

省電休眠模式,且可寬電壓運行(5-2.7V),抗干擾能力強,可降低一般8位機中的軟體抗干擾設計工作量和硬體的使用量。

AVR系列單片機的選型

AVR單片機系列齊全,可適用於各種不同場合的要求。

AVR單片機有3個檔次:

低檔Tiny系列:主要有Tiny11/12/13/15/26/28等;

中檔AT90S系列:主要有AT90S1200/2313/8515/8535等;(正在淘汰或轉型到Mega中)

高檔ATmega:主要有ATmega8/16/32/64/128(存儲容量為8/16/32/64/128KB)以及ATmega8515/8535等。

AVR器件引腳從8腳到64腳,還有各種不同封裝供選擇。

優勢特徵

高可靠性、功能強、高速度、低功耗和低價位,一直是衡量單片機性能的重要指標,也是單片機占領市場、賴以生存的必要條件。

最大特點

與其它8-Bit MCU相比,AVR 8-Bit MCU最大的特點是:

哈佛結構,具備1MIPS / MHz的高速運行處理能力;

超功能精簡指令集(RISC),具有32個通用工作暫存器,克服了如8051 MCU採用單一ACC進行處理造成的瓶頸現象;

快速的存取暫存器組、單周期指令系統,大大最佳化了目標代碼的大小、執行效率,部分型號FLASH非常大,特別適用於使用高級語言進行開發;

作輸出時與PIC的HI/LOW相同,可輸出40mA(單一輸出),作輸入時可設定為三態高阻抗輸入或帶上拉電阻輸入,具備10mA-20mA

灌電流的能力;

片內集成多種頻率的

RC振盪器、上電自動復位、看門狗、啟動延時等功能,外圍電路更加簡單,系統更加穩定可靠;

大部分AVR片上資源豐富:帶E2PROM,PWM,RTC,SPI,

UART,TWI,ISP,AD,Analog Comparator,

WDT等;

大部分AVR除了有ISP功能外,還有IAP功能,方便升級或銷毀應用程式。

結構分類

型號標識

⒈型號緊跟的字母,表示電壓工作範圍。帶“V”:1.8-5.5V;若預設,不帶“V”:2.7-5.5V。

例:ATmega48-20AU,不帶“V”表示工作電壓為2.7-5.5V。

例:ATmega48-20AU,“20”表示可支持最高為20MHZ的系統時鐘。

⒊後綴第一(第二)個字母,表示封裝。“P”:DIP封裝,“A”:

TQFP封裝,“M”:MLF封裝。

例:ATmega48-20AU,“A”表示TQFP封裝。

⒋後綴最後一個字母,表示套用級別。“C”:商業級,“I”:工業級(有鉛)、“U”工業級(無鉛)。

例:ATmega48-20AU,“U”表示無鉛工業級。ATmega48-20AI,“I”表示有鉛工業級。

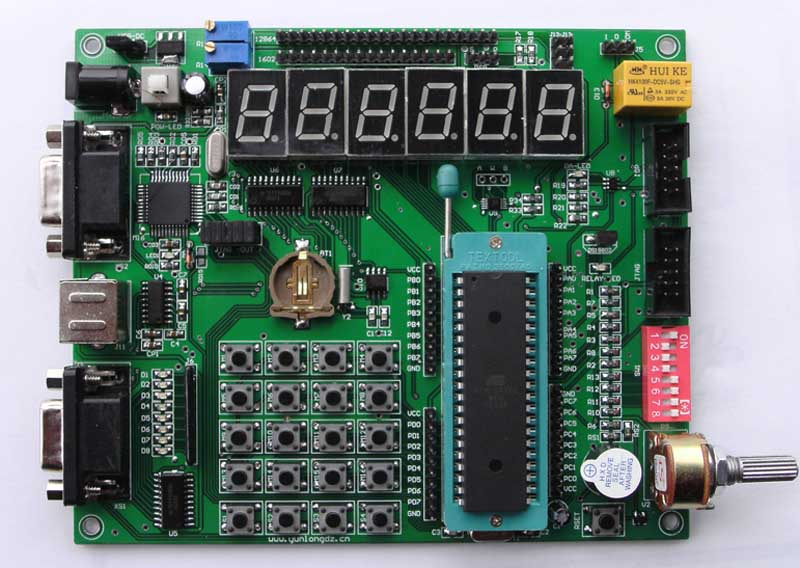

接口設計

USB接口以其數據傳輸快、連線簡單、易於擴展、支持

熱插拔等特點已成為外設與PC通信的主要方式之一。隨著

嵌入式系統的發展,

嵌入式微處理器需增加通用的USB接口,以便實現與PC等USB

主機系統的通信。針對這樣的需求,這裡採用PHILIPS公司的USB接口器件PDIUSBD12和Atmel公司的AVR系列

單片機ATmega8設計一種通用的USB接口模組。該模組可方便為各種嵌入式微處理器增加USB接口,從而實現與USB主機系統的高速通信。

系統硬體設計

該系統模組的控制核心是AVR高速

單片機ATmega8。AVR單片機是新一代基於

哈佛結構的高速RISC微控制器,具有速度快、價格低、可靠性高,I/O口線驅動能力強和片內集成外設資源豐富等特點,其內部集成有可進行ISP下載編程的Flash,EEPROM、

熔絲位和鎖定位。AVR單片機的ISP下載電纜製作簡單、成本低廉,還有免費的

下載軟體(例如PonyProg)支持。PDIUSBD12是一款高性價比USB接口器件,完全符合USB1.l規範,易於與各種

微處理器接口。

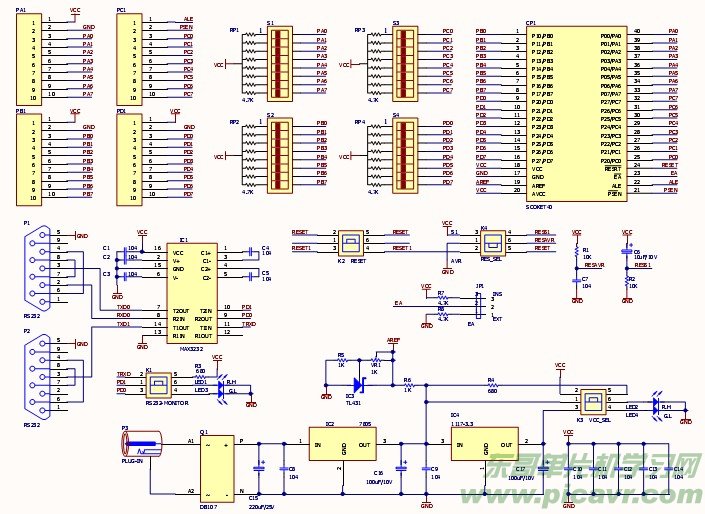

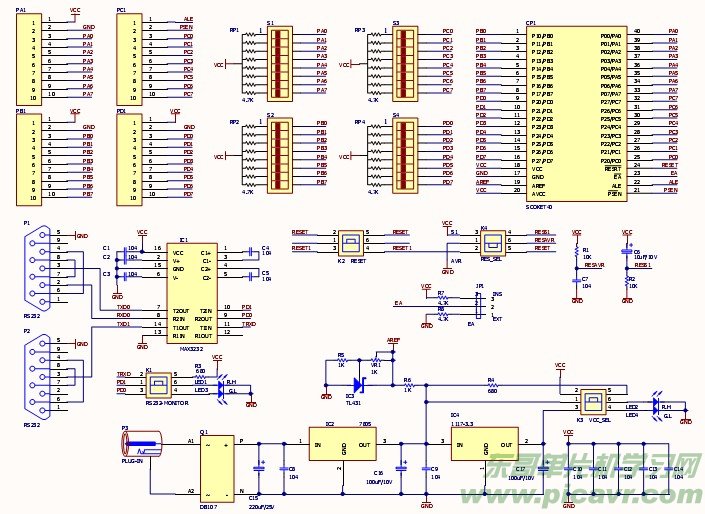

系統模組AVR單片機與PDIUSBD12的電路連線如圖1所示。

由圖1看出,由於AVR

單片機具有高速性,可利用I/O連線埠線以軟體方式模擬PDIUSBD12的時序,對其讀寫。這種方式可根據不同的微處理器速度靈活控制PDIUSBD12的時序和地址,無需解碼電路,從而簡化硬體設計,降低成本。

由於ATmega8片內集成了UART,SPI,I2C等接口,該接口模組可利用這些接口與其他系統通信,使得該接口模組成為通用的

接口轉換器。其系統硬體結構框圖如圖2所示。

USB固件程式

USB固件程式設計

本系統模組的USB固件程式採用符合ANSI C標準的GCC編譯器設計,結合分層次的模組化結構,可移植性強,只需稍微修改硬體接口層即可將其移植到別的硬體平台,可重複利用代碼。USB固件程式設計是基於

狀態機和標準的前後台式程式架構。整個同件程式的模組化層次結構如圖3所示。首先編寫硬體接口層hal.c和PDIUSBD12器件的命令接口層,以供上層模組調用。硬體接口層含有對PDIUSBD12寫指令和讀寫數據的函式,以供上層模組調用。當CPU不同時,只需修改這些函式即可。由於CPU訪問PDIUS-BD12與普通

存儲器一樣,只需根據硬體連線關係,在

硬體抽象層中編寫對PDIUSBD12寫指令、寫讀數據的函式,供上層調用即可。實現PDIUSBD12的命令接口層需調用硬體抽象層函式,供上層模組調用。再設計前後台程式及標準設備請求

程式模組。

用途套用

市場角度

套用區域

AVR已被廣泛用於:

空調控制板

印表機控制板

智慧型電錶

LED控制屏

醫療設備

GPS

注意問題

寫用PORTx,讀取用PINx

實驗時,儘量不要把管腳直接接到GND/VCC,當設定不當,IO口將會輸出/灌入 80mA(Vcc=5V)的大電流,導致器件損壞。

作輸入時:

1通常要使能內部上拉電阻,懸空(高阻態)將會很容易受干擾。(表面看好像是51的抗干擾能力強,是因為51永遠有內部電阻上拉,)

2儘量不要讓輸入懸空或模擬輸入電平接近VCC/2,將會消耗太多的電流,特別是低功耗套用場合------CMOS電路的特點

3讀取軟體賦予的引腳電平時需要在賦值指令out 和讀取指令in 之間有一個時鐘周期的間隔,如nop 指令。

4功能模組(中斷,定時器)的輸入可以是低電平觸發,也可以是上升沿觸發或下降沿觸發。

5用於高阻模擬信號輸入,切記不要使能內部上拉電阻,影響精確度。例如ADC數模轉換器輸入,模擬比較器輸入

作輸出時:

採用必要的限流措施,例如驅動LED要串入限流電阻

復位時:

復位時內部上拉電阻將被禁用。如果套用中(例如電機控制)需要嚴格的電平控制,請使用外接電阻固定電平

休眠時:

作輸出的,依然維持狀態不變

作輸入的,一般無效,但如果使能了第二功能(中斷使能),其輸入功能有效。例如 外部中斷的喚醒功能。