在高階合成中,暫存器轉移級或門級電路由具有高階抽象的行為性描述(如算法)的電路合成。

基本介紹

- 中文名:高階合成

- 外文名:High level synthesis

- 套用學科:通信科技

在高階合成中,暫存器轉移級或門級電路由具有高階抽象的行為性描述(如算法)的電路合成。

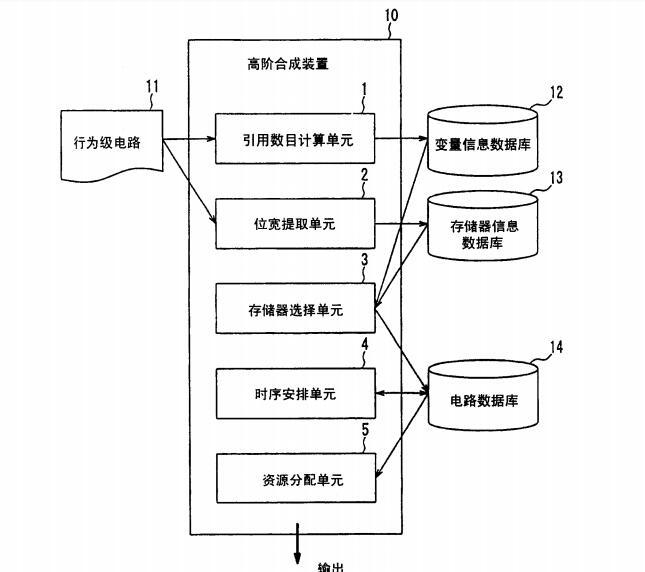

在高階合成中,暫存器轉移級或門級電路由具有高階抽象的行為性描述(如算法)的電路合成。高階合成方法高階合成方法最好具有:CDFG生成步驟、CDFG安排步驟、分配步驟、時鐘安排步驟、重新定時步驟。在CDFG生成步驟中,把動作...

《新型納米原子簇聚合物合成和高階非線性光學研究》是依託南京大學,由鄭和根擔任項目負責人的面上項目。項目摘要 本課題我們將在已經取得的前期成果基礎上,進一步設計合成幾大類結構新穎的橋連配體,通過與某些金屬離子的配位自組裝或可控...

本項目的開展有望為複雜機械互鎖結構——特別是高階[n]索烴——的製備探索一條新思路,並實現它們在分子機器和超分子聚合物等領域中的套用。結題摘要 本項目針對多組分高階索烴製備困難的問題,設計、合成了一系列新型的冠醚、基於冠醚...

超能度2的接觸感應能力者。因為經濟關係而接受學校的改造人類細胞實驗,啟發了隱藏的能力,同時產生了另一人格,名叫「卡莉」。卡莉是高階合成能力ESP,包括念動力、瞬間移動、預知能力和精神感應能力等。帝國陸軍超能特務部隊 成員:伊 九...

2.套裝的高階合成.(現在原有的6套套裝可以在創造圖騰合成為新的高級套裝.並且根據物品籃第一位的套裝分別合成不同的高級套裝.)3.動態怪物初步測試.(玩家在遊戲中擊敗某個單位有可能影響將要面對的怪物的變化.目前在測試階段.因此只有...

執政官是暴雪娛樂公司出品的即時戰略遊戲《星際爭霸》中的星靈單位。高階聖堂武士合成執政官後,就不能再變回原樣了。執政官的本體十分脆弱,一旦護盾被消耗完,執政官就非常容易死亡,所以在面對很多執政官的時候,科技球的EMP震盪波是...

特權化、權利傾向、虛情假意、過分樂觀、認知怠惰、半途而廢,和兩個效度量表,混銷量表和防禦量表,在此基礎上還衍生出兩個內容量表當前的犯罪思維和過往的犯罪思維,四個子量表問題迴避、低頻率、自我斷言、拒絕傷害,兩個高階的合成...

翅膀合成:1、通過“合成系統”進入翅膀合成。2、合成高階的翅膀需要消耗兩個低階的翅膀和一定數量的靈羽,機率成功,成功後隨機生成極品屬性。合成翅膀材料的獲得:1、陣營戰可使用“浴血石”兌換1階天空之翼和靈羽。2、世界BOSS和極...

書中循序漸進地講解了數碼照片處理的入門工具、基本原理、高階合成技術,為讀者使用Photoshop進行數碼照片藝術設計提供學習和參考範例。《數碼照片藝術化處理聖經(全彩)》可為家庭用戶、個人數碼愛好者和專業影樓提供最貼身、最實用的數碼照片...

高階寶石 高階寶石合成 在《星世紀》中,將增加新的寶石合成,可以在聯邦/帝國陣營強化處就可以找到對應NPC。其中,低階的寶石合成,只能有幾率合成普通非凡寶石、優良非凡寶石、精緻非凡寶石。失敗後寶石將消失。高階的寶石合成,就是《...

短劍,是MOBA競技網遊《英雄聯盟》中的裝備。提供攻擊速度,能合成高階的攻速裝備。裝備屬性 總花費:300金幣 攻擊速度:12% 出售價格:210金幣 裝備合成 可合成裝備:基舍艾斯碎片(700金幣)、反曲之弓(1000金幣)、狂戰士脛甲(1100...

高階裝備合成獲取 坐騎 各種腦洞騎寵設定都能在遊戲中體驗到,不同坐騎皮膚帶來不同加成 裝備融合 多餘的低階裝備不要扔,可以融合成高階裝備 裝備進階 多餘的低階裝備不要扔,可以進階成高階裝備 時裝 極品時裝擊殺boss獲取 拼的就...

遠古兵器 (Ancient Weaponary)是指基於魔獸爭霸3:冰封王座(由暴雪娛樂公司出品)的多人即時對戰自定義地圖DotA中的一個中立商店的名字,天災軍團和近衛軍團各有一個。此商店出售一些中高階的合成物品捲軸,多為提高DPS能力的裝備。包括...

D階寵物一定幾率可以合成C階寵物,依次類推,低階寵物靠合成可以得到高階寵物。寵物升級最高50級。寵物滿級之後,我們要做的是強化,強化最高15級。一個強大的寵物可以提升極高的戰力,可以給予不同的增益狀態。寵物的等級最高為Lv....

例如:玩家希望合成高階武器劍,則儘量用劍類武器作為主裝備進行合成,希望合成高階法袍,則儘量用法袍作為主裝備進行合成,其他武器及防具類似,但需要注意的是,主裝備影響合成後裝備的形象,但不等於決定合成後裝備的形象,所以是一個...

這個功能主要是用於用低階寶石合成高階寶石,只要你收集到最後多的低階寶石,你就可以將他們合成為同類型寶石中的高階產品。洗鍊 在裝備洗鍊功能中,玩家可以消耗元寶對裝備進行洗鍊,每件裝備最多可獲得3條加成屬性,其中更有隱藏屬性等...

Subleq2也可用於合成高階指令,儘管它通常需要針對給定任務執行更多操作。例如,轉換給定位元組中的所有位需要不少於10個subleq2指令:NOT a 仿真 以下程式(以偽代碼編寫)模擬基於subleq的OISC的執行:該程式假定memory[]由非負整數索引。

遊戲攻略 14級可以合成、鑲嵌寶石。寶石可以大幅度增加玩家的戰鬥力。寶石分為攻擊、生命、命中、閃避、物防、法防6種。低階的寶石可以合成為高階的寶石,鑲嵌的寶石品階越高,玩家在戰鬥中越輕鬆。