專利背景

流水線模數轉換器(ADC)因擁有高速、高精度、低功耗和晶片占用面積小的優勢而被廣泛套用於寬頻通訊系統以及視頻圖像處理。流水線ADC轉換電路如圖1所示,它由N級結構相同的流水線子級轉換電路101A、101B、…、101N和全並行模數轉換器(Flash ADC)電路102構成。模擬信號VIN被送到第一級流水線轉換電路(圖1中記為stage1)101A作為輸入信號,經過第一級流水線轉換電路101A的模數轉換後,所述第一級流水線模數轉換電路101A輸出k(1)比特(bit)的數字碼和殘差模擬電壓Vres1。所述殘差模擬電壓Vres1接著被送到第二級流水線轉換電路101B(圖1中記為stage2)進行轉換並輸出k(2)比特的數字碼和殘差模擬電壓Vres2。由此流水工作,可得到各級數字輸出碼,其中第N級流水線轉換電路101N(圖1中記為stageN)輸出k(N)比特的數字碼和殘差模擬電壓VresN至全並行模數轉換器電路102,經過全並行模數轉換器電路102處理之後,得到k(N+1)比特的數字碼並最終輸出至後端電路。

圖2是流水線子級轉換電路101A、101B、…、101N中的每一子級電路的具體結構,它包括採樣/保持電路(S/H)201、減法電路(SUB)202、增益放大電路(Gain)203、低精度模數轉換器(Sub-ADC)204和低精度數模轉換器(Sub-DAC)205。它的工作原理是:上一子級轉換電路的輸出信號作為本子級轉換電路的輸入信號Vi(對於第一子級轉換電路101A,輸入信號Vi就是流水線ADC的輸入VIN),本子級轉換電路中的採樣/保持電路201對輸入信號Vi進行採樣,同時低精度模數轉換器204對輸入信號Vi進行模數轉換,轉換後得到的k比特的數字碼作為本子級轉換電路的數字輸出碼,同時輸出到低精度數模轉換器205以實現對輸入信號Vi的估計。輸入信號Vi與估計值經減法電路202處理,所得的殘差電壓經增益放大電路203進行放大,得到本子級殘差輸出模擬電壓Vres,作為後一子級轉換電路的輸入信號。在電路實現中,通常將採樣/保持電路201、減法電路202、增益放大電路203和低精度數模轉換器205結合在一起,用開關電容電路來實現,這種電路被叫做乘法型數模轉換器(Multiplying Digital-to-Analog Converter,MDAC)。

圖3是MDAC的具體電路。為了保證更好的電容匹配度,MDAC由基於單位電容陣列的開關電容電路實現。如圖3所示,MDAC由電容陣列301、殘差運算放大器(Residue Amplifier,RA)302和開關構成,且整個MDAC在採樣相Ф1和放大相Ф2的控制下工作。其中Ф1和Ф1e為採樣相時鐘信號,Ф2為反饋相時鐘信號,工作時用於控制採樣時鐘信號Ф1e的開關先於控制採樣時鐘信號Ф1的開關被閉合,且高電平有效(圖4為採樣相時鐘信號Ф1、Ф1e以及反饋相時鐘信號Ф2的工作時序圖)。電容陣列301中所有電容(包括採樣電容Cf1、Cf2及反饋電容Cs1、Cs2)的上極板都連線殘差運算放大器302的輸入端,而電容的下極板根據其電路連線方式,可以分為四類。

採樣電容Cs1由x1個單位電容C組成,採樣相時連線輸入信號Vi,對輸入信號Vi進行採樣,放大相時根據比較器的輸出碼控制選擇開關是否導通以連線基準電平DVR;採樣電容Cs2由x2個單位電容C組成,採樣相時連線輸入信號Vi,對輸入信號Vi進行採樣,放大相時接交流地;反饋電容Cf1由x3個單位電容C構成,採樣相時連線輸入信號Vi,對輸入信號Vi進行採樣,放大相時接到殘差運算放大器302輸出殘差模擬電壓Vres;反饋電容Cf2由x4個單位電容C構成,採樣相和放大相時都連線殘差運算放大器302輸出殘差模擬電壓Vres。通過選擇不同電路連線方式的電容(Cs1、Cs2、Cf1、Cf2)以及不同電容的單元電容個數(x1、x2、x3、x4),可以實現滿足不同需求的MDAC的傳輸函式。

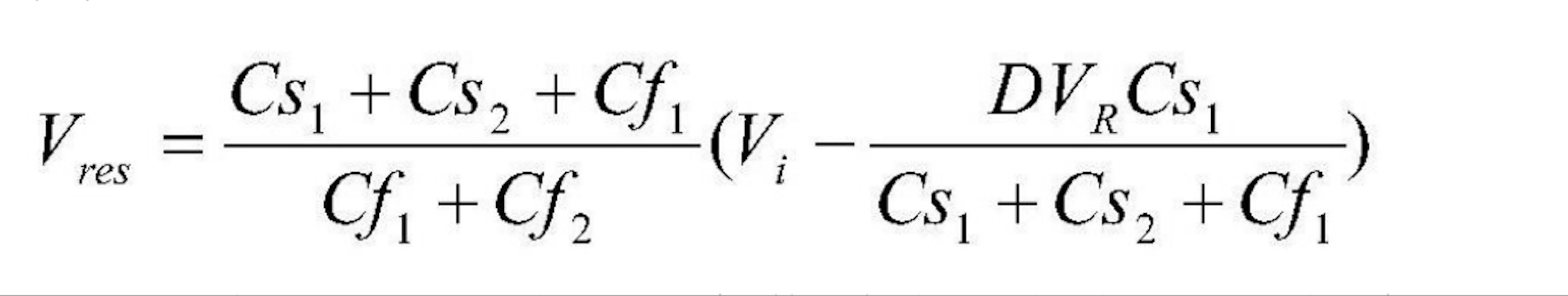

根據電荷守恆,可以得到在忽略殘差運算放大器302的增益誤差的情況下,MDAC的傳輸函式為:

可以看到,MDAC的傳輸曲線的增益就是電容Cs1、Cs2、Cf1之和與電容Cf1、Cf2之和的比例,理想情況下,也就是(x1+x2+x3)/(x3+x4),這就要求用於構成每種電容的單元電容的大小C是相同的,否則,會引起增益誤差,影響MDAC的性能。同理,傳輸曲線的DAC電平與電容之比DCs1/(Cs1+Cs2+Cf1)也與單元電容的大小C相關,如果這些類型的單元電容大小C不同,產生失配,那么DAC電平會出現偏差,每個電容貢獻的權重不同,同樣會影響MDAC的性能,嚴重時甚至影響ADC的功能。

電容失配誤差主要分為系統誤差和隨機誤差。系統誤差可以通過合理的版圖設計消除或減小。電容失配系統誤差主要由以下四個因素引起:(1)光刻引起周長比例不匹配;(2)刻蝕率不同引起的不匹配;(3)氧化層梯度效應;(4)寄生電容的不匹配。

針對誤差因素(1),如果電容的周長比與面積比相等,則可以消除此影響,因此通過將單位電容並聯實現大電容的方法來解決。針對誤差因素(2),可以在電容陣列外圍加上虛擬(dummy)電容,使得每個單位電容周圍的版圖環境儘可能相同。針對誤差因素(3),傳統的版圖設計方法通常採用單位電容陣列共心的版圖布局,這樣就減小了氧化層梯度對電容匹配精度的影響。然而,這種設計方法只適合於需要電容匹配的類型少的情況。隨著需要電容匹配的類型的增加,共心版圖設計變得越來越繁瑣,布局布線越來越複雜,使得引線電容和外引線寄生電容增加,並且加大了寄生電容不匹配因素,同時會浪費晶片面積。

對於誤差因素(4),版圖上電容的上極板和下極板與鄰近電容的走線之間會存在大量的寄生電容,使得單元電容的實際值CA不等於自身電容C,而是自身電容C與寄生電容Cp之和,如圖5a所示。圖5b中,當電容附近有一條金屬走線時,則電容的上下極板都會與該金屬連線形成寄生電容Cp。圖5c中,通過引線給上極板加電位時,引線和多出來的這部分下極板也形成了寄生電容Cp。MDAC電容陣列布局布線的不同,會導致每個單位電容的寄生電容Cp不同,使得實際的單位電容CA不一致,造成電容不匹配,從而引起MDAC傳輸曲線的增益誤差和DAC誤差,會嚴重影響MDAC的性能,從而降低整個ADC的線性度,嚴重時甚至影響ADC的功能。

隨著MOS工藝的提高,電容尺寸越來越小,寄生電容越來越明顯,甚至比單位電容還大,因此,先進工藝下對電容陣列的版圖布局布線提出了更高的要求。而MDAC電容陣列布局會受到版圖面積限制。因此,如何在有限面積下對電容陣列進行版圖設計,消除寄生電容引起的電容失配誤差,產生匹配的電容陣列,是一個關鍵問題和設計難題。

發明內容

專利目的

《電容陣列及其版圖設計方法》所要解決的技術問題是在有限版圖面積下,提供一種產生匹配單位電容陣列的版圖設計方法以及一種電容陣列。該發明不僅消除了由寄生電容引起的電容比例失配誤差,以使電容陣列匹配,而且操作簡單方便,實現的電容陣列占用晶片版圖面積小,特別適用於高精度流水線ADC,也可以推廣套用到電容陣列匹配要求高的數模轉換器,開關電容濾波器等。

技術方案

第一方面,《電容陣列及其版圖設計方法》提供了一種電容陣列版圖設計方法,其中電容陣列包括第一類至第K類電容(K為大於或等於1的整數),每一電容包括若干單位電容,所述電容陣列版圖設計方法包括以下步驟:

確定單位電容布線方式:使得每一單位電容的上極板連線和下極板連線相互平行,且每一單位電容的下極板連線統一由同種金屬線相連,所述金屬線對稱分布在各單位電容的下極板的兩側,每一單位電容的上極板連線統一由同種金屬線相連且位於單位電容的中心;

確定電容陣列布局:所述電容陣列的列數和行數分別為M和N,且所述電容陣列包括內部電容陣列和外部虛擬電容陣列,所述外部虛擬電容陣列由若干虛擬電容組成且位於內部電容陣列的四周,所述內部電容陣列包括兩個完全對稱的單邊內部電容陣列,a、確定單邊內部電容陣列的列數的最大值Mh,Mh=M/2-Mdx,Mh取整數,其中Mdx表示外部虛擬電容陣列的列數,且Mdx≥1.5,b、確定單邊內部電容陣列中第一類至第K類電容在版圖布局中的列數,c、對電容陣列中的電容進行布局,其中第一類至第K類電容的列數之和不大於Mh,且每一列電容中至多包括兩種不同電路連線方式的電容;

電容陣列布線:使得每一單位電容的上下極板連線的並行長度一致;以及對版圖進行寄生參數提取,驗證電容陣列版圖設計是否滿足匹配要求。

其中,所述步驟“確定電容陣列布局”中,其中所述步驟“b、確定單邊內部電容陣列中第一類至第K類電容在版圖布局中的列數”:如果其中一類電容的單位電容具有不同的電路連線方式且該類電容由x1個單位電容組成,則該類電容在版圖布局中的最小列數等於x1/2。

其中,所述步驟“確定電容陣列布局”中,確定Mh及每一類電容在版圖布局中的列數之後,單邊內部電容陣列中空白的地方使用虛擬電容補齊。

其中,當一列電容中有兩種不同電路連線方式的電容時,分布於單位電容的下極板的兩條金屬線中只有一條金屬線通過通孔連線到該單位電容的下極板。

其中,當一列電容中只有一種電路連線方式的電容時,分布於單位電容的下極板的兩條金屬線均通過通孔連線到下極板。

第二方面,《電容陣列及其版圖設計方法》還提供了一種電容陣列,包括M列和N行電容,所述電容陣列包括內部電容陣列和外部虛擬電容陣列,所述外部虛擬電容陣列由若干虛擬電容組成且位於內部電容陣列的四周,所述內部電容陣列包括兩個完全對稱的單邊內部電容陣列且包括第一類至第K類電容(K為大於或等於1的整數),其中每一電容均由若干單位電容組成,每一單位電容的上極板連線和下極板連線相互平行,且每一單位電容的下極板連線統一由金屬線相連,所述金屬線對稱分布在各單位電容的下極板的兩側,每一單位電容的上極板連線統一由同種金屬線相連且位於單位電容的中心,且所述每一單位電容的上下極板連線的並行長度一致;所述單邊內部電容陣列中列數的最大值為Mh,Mh=M/2-Mdx,Mh取整數,其中Mdx表示外部虛擬電容的列數,且Mdx≥1.5;所述單邊內部電容陣列中第一類至第K類電容的列數之和不大於Mh且每一列電容中至多包括兩種不同電路連線方式的電容。

其中,如果其中一類電容的單位電容具有不同的電路連線方式且該類電容由x1個單位電容組成,則該類電容在版圖布局中的最小列數等於x1/2。

其中,所述單邊內部電容陣列中除去第一類至第K類電容之外空白的地方均為虛擬電容。

其中,當一列電容中有兩種不同電路連線方式的電容時,分布於單位電容的下極板的兩條金屬線中只有一條金屬線通過通孔連線到該單位電容的下極板。

其中,當一列電容中只有一種電路連線方式的電容時,分布於單位電容的下極板的兩條金屬線均通過通孔連線到下極板。

上述電容陣列及版圖布局方法不僅消除了由寄生電容引起的電容比例失配誤差,以使電容陣列匹配,而且操作簡單方便,實現的電容陣列占用晶片版圖面積小,特別適用於高精度流水線ADC,也可以推廣套用到電容陣列匹配要求高的數模轉換器,開關電容濾波器等。

附圖說明

圖1為2013年之前的流水線模數轉換器的電路示意圖。

圖2為圖1中每一流水線子級轉換電路的電路示意圖。

圖3為圖2中單位電容陣列乘法型數模轉換器(MDAC)的具體電路圖。

圖4為圖3中單位電容陣列乘法型數模轉換器的採樣相時鐘信號以及反饋相時鐘信號的工作時序圖。

圖5a-5c為2013年之前的單位電容的寄生電容來源示意圖。

圖6為《電容陣列及其版圖設計方法》電容陣列的較佳實施方式的示意圖。

圖7為《電容陣列及其版圖設計方法》電容陣列版圖設計方法的較佳實施方式的流程示意圖。

圖8為單位電容布線方法的示意圖。

圖9為電容陣列布局的示意圖。

圖10為《電容陣列及其版圖設計方法》電容陣列的布局示意圖。

圖11為單位電容的寄生電容說明示意圖。

圖12為《電容陣列及其版圖設計方法》電容陣列布線的示意圖。

技術領域

《電容陣列及其版圖設計方法》涉及電力領域,具體指一種電容陣列和版圖的設計方法。

權利要求

1.一種電容陣列版圖設計方法,其中電容陣列包括第一類至第K類電容(K為大於或等於1的整數),每一電容包括若干單位電容,其特徵在於:所述電容陣列版圖設計方法包括以下步驟:確定單位電容布線方式:使得每一單位電容的上極板連線和下極板連線相互平行,且每一單位電容的下極板連線統一由同種金屬線相連,所述金屬線對稱分布在各單位電容的下極板的兩側,每一單位電容的上極板連線統一由同種金屬線相連且位於單位電容的中心;確定電容陣列布局:所述電容陣列的列數和行數分別為M和N,且所述電容陣列包括內部電容陣列和外部虛擬電容陣列,所述外部虛擬電容陣列由若干虛擬電容組成且位於內部電容陣列的四周,所述內部電容陣列包括兩個完全對稱的單邊內部電容陣列,a、確定單邊內部電容陣列的列數的最大值Mh,Mh=M/2-Mdx,Mh取整數,其中Mdx表示外部虛擬電容陣列的列數,且Mdx≥1.5,b、確定單邊內部電容陣列中第一類至第K類電容在版圖布局中的列數,c、對電容陣列中的電容進行布局,其中第一類至第K類電容的列數之和不大於Mh,且每一列電容中至多包括兩種不同電路連線方式的電容;電容陣列布線:使得每一單位電容的上下極板連線的並行長度一致;以及對版圖進行寄生參數提取,驗證電容陣列版圖設計是否滿足匹配要求。

2.如權利要求1所述的電容陣列版圖設計方法,其特徵在於:所述步驟“確定電容陣列布局”中,其中所述步驟“b、確定單邊內部電容陣列中第一類至第K類電容在版圖布局中的列數”:如果其中一類電容的單位電容具有不同的電路連線方式且該類電容由x1個單位電容組成,則該類電容在版圖布局中的最小列數等於x1/2。

3.如權利要求1或2所述的電容陣列版圖設計方法,其特徵在於:所述步驟“確定電容陣列布局”中,確定Mh及每一類電容在版圖布局中的列數之後,單邊內部電容陣列中空白的地方使用虛擬電容補齊。

4.如權利要求1所述的電容陣列版圖設計方法,其特徵在於:當一列電容中有兩種不同電路連線方式的電容時,分布於單位電容的下極板的兩條金屬線中只有一條金屬線通過通孔連線到該單位電容的下極板。

5.如權利要求1所述的電容陣列版圖設計方法,其特徵在於:當一列電容中只有一種電路連線方式的電容時,分布於單位電容的下極板的兩條金屬線均通過通孔連線到下極板。

6.一種電容陣列,包括M列和N行電容,其特徵在於:所述電容陣列包括內部電容陣列和外部虛擬電容陣列,所述外部虛擬電容陣列由若干虛擬電容組成且位於內部電容陣列的四周,所述內部電容陣列包括兩個完全對稱的單邊內部電容陣列且包括第一類至第K類電容(K為大於或等於1的整數),其中每一電容均由若干單位電容組成,每一單位電容的上極板連線和下極板連線相互平行,且每一單位電容的下極板連線統一由金屬線相連,所述金屬線對稱分布在各單位電容的下極板的兩側,每一單位電容的上極板連線統一由同種金屬線相連且位於單位電容的中心,且所述每一單位電容的上下極板連線的並行長度一致;所述單邊內部電容陣列中列數的最大值為Mh,Mh=M/2-Mdx,Mh取整數,其中Mdx表示外部虛擬電容的列數,且Mdx≥1.5;所述單邊內部電容陣列中第一類至第K類電容的列數之和不大於Mh且每一列電容中至多包括兩種不同電路連線方式的電容。

7.如權利要求6所述的電容陣列,其特徵在於:如果其中一類電容的單位電容具有不同的電路連線方式且該類電容由x1個單位電容組成,則該類電容在版圖布局中的最小列數等於x1/2。

8.如權利要求6或7所述的電容陣列,其特徵在於:所述單邊內部電容陣列中除去第一類至第K類電容之外空白的地方均為虛擬電容。

9.如權利要求6所述的電容陣列,其特徵在於:當一列電容中有兩種不同電路連線方式的電容時,分布於單位電容的下極板的兩條金屬線中只有一條金屬線通過通孔連線到該單位電容的下極板。

10.如權利要求6所述的電容陣列,其特徵在於:當一列電容中只有一種電路連線方式的電容時,分布於單位電容的下極板的兩條金屬線均通過通孔連線到下極板。

實施方式

由於MDAC電容陣列完全對稱,所以《電容陣列及其版圖設計方法》以單邊電容陣列的版圖為例來闡述流水線ADC中的電容陣列版圖設計方法。得到單邊電容陣列版圖後,另外一邊版圖完全對稱即可。

假設電容陣列在版圖中的列數和行數分別為M和N,如圖6所示。M表示與信號流垂直的電容個數,N表示與信號流方向平行的電容個數。M及N均為0.5的整數倍。當M、N為0.5的奇數倍時,表示採用了半個虛擬電容。如圖6所示,電容陣列版圖包括內部電容陣列(標識線61以內的所屬電容陣列)和外部虛擬電容陣列(標識線61與標識線62之間的所屬電容陣列),所述外部虛擬電容陣列位於內部電容陣列的四周。所述內部電容陣列是針對電路中的若干類電容的版圖,特別地,在圖3中是指電容Cs1、Cs2、Cf1、Cf2的版圖。由於圖3中MDAC電容陣列完全對稱,因此所述內部電容陣列包括兩個完全對稱的單邊內部電容陣列。

《電容陣列及其版圖設計方法》的具體實施方式不僅限於下面的描述,現結合附圖加以進一步說明。

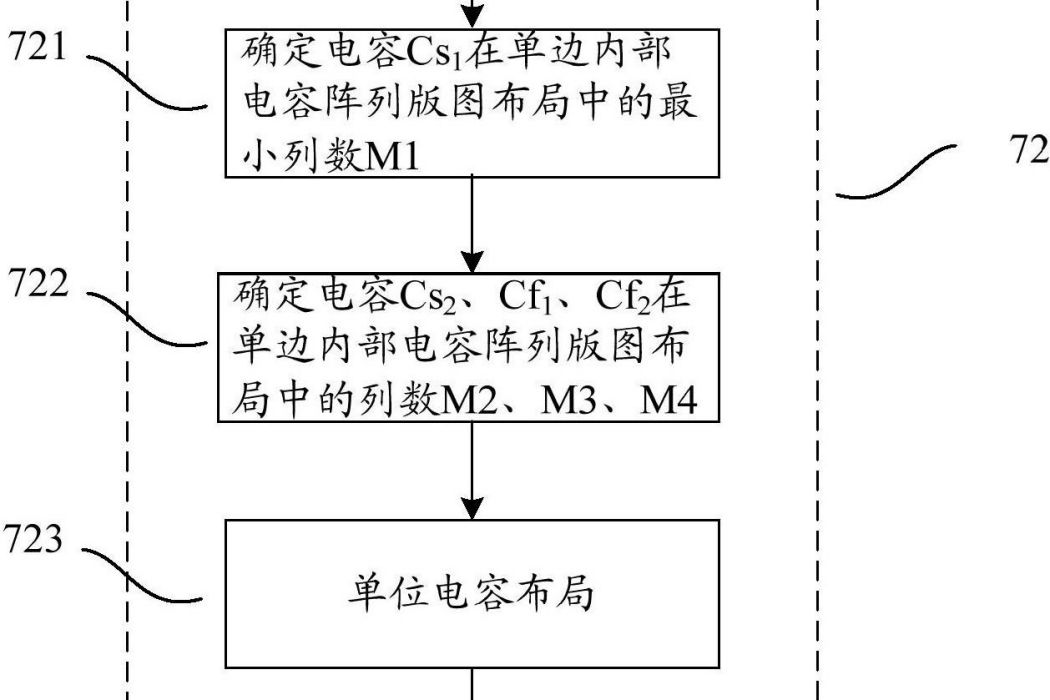

《電容陣列及其版圖設計方法》提出了一種在有限版圖面積下,產生匹配單位電容陣列的版圖設計方法,圖7是該發明的設計流程圖。可以理解的是,雖然該設計流程主要針對流水線ADC中的電容陣列版圖設計方法,但亦可擴展到對電容陣列匹配精度要求高的數模轉換器、開關電容濾波器等。設計流程主要分解為四個步驟:步驟71:確定單位電容布線方式;步驟72:確定電容陣列布局,特別地,在流水線ADC中是確定電容Cs1、Cs2、Cf1、Cf2的版圖布局;步驟73:電容陣列布線;步驟74:對版圖進行寄生參數提取,驗證電容陣列版圖設計是否滿足匹配要求。當然,該實施方式中所提到的電容Cs1、Cs2、Cf1、Cf2僅為針對流水線ADC中的電容陣列版圖的一示例。在其他流水線ADC的電容陣列中,還有可能只包含兩類電容(Cs1&Cf1、Cs1&Cf2等等),或者三類電容(Cs1&Cs2&Cf1等等)。另外,當這種電容版圖設計方法套用於電容陣列匹配要求高的數模轉換器、開關電容濾波器等時,電容的分類就不是Cs1、Cs2、Cf1、Cf2了,也可能甚至沒有採樣電容和反饋電容的說法。但是,整個電容版圖的設計原則是相同的,只不過電容的分類不一樣而已。至於電容的分類則根據具體電路來選定。甚至於其他實施方式中,整個電容版圖中亦可只包括一種電容。

具體的,所述步驟72(確定電容陣列布局)又分為四個子步驟:

步驟720:確定單邊內部電容陣列版圖的列數的最大值Mh;

步驟721:確定電容Cs1在單邊內部電容陣列版圖布局中的最小列數M1;

步驟722:確定電容Cs2、Cf1和Cf2在單邊內部電容陣列版圖布局中的列數M2、M3和M4;當然,如果整個電容版圖中只包括一種電容,此步即可省略,即只需確定Mh和M1即可。

步驟723:對電容陣列中的單位電容進行布局。設計流程中的每個步驟都是產生匹配電容陣列版圖的不可缺少的一個任務,下面將對每個任務的設計準則和方法進行詳細闡述。

圖8是步驟71的具體實現方式。電容的上極板連線和下極板連線都與信號流的方向平行。電容的下極板連線統一由金屬鋁線1進行連線,金屬鋁線1對稱分布在下極板的兩側。當外部信號與該電容的下極板相連線時,金屬鋁線1通過打孔10連線到下極板。需要注意的是兩條金屬鋁線1都連線到下極板,或者只有一條金屬鋁線1連線到下極板是有講究的,具體方法在步驟73中進行詳細闡述。當外部信號與該電容的下極板不相連線時,則不需打孔。電容的上極板連線則統一由金屬鋁線2進行連線,位於電容中心。在流水線ADC中,電容陣列中的所有電容,也就是電容Cs1、Cs2、Cf1和Cf2的布線方式都按照圖8所示的布線方式進行。

單位電容布線方式統一,使得每個單位電容的周圍環境都相同,同時,電容上極板連線和下極板連線都與信號流方向平行(即電容的上極板連線和下極板連線相互平行),並且都固定在單位電容面積內,不僅減小了光刻引起周長比例不匹配和刻蝕率不同引起的不匹配所帶來的電容失配誤差,而且使得整個電容陣列版圖布線不會凌亂,減小了版圖面積,也讓版圖看起來非常美觀。

特別地,單位電容的下極板連線通過兩條金屬鋁線1與外部相連,也就限制了版圖上每一列電容可以與外界連線的信號個數最多只能是兩個。

步驟72是指在有限版圖面積下,根據電容的電路連線特性分類布局成列。流水線ADC中有四類電容Cs1、Cs2、Cf1和Cf2,下面分別講述每種電容在版圖布局中列數確定的方法以及整體布局方法。

首先,步驟720:確定單邊內部電容陣列版圖列數最大值Mh。如圖6中所示,電容陣列版圖中,為了讓每個單位電容的周圍環境儘量相同,需要在內部電容陣列四周布局至少1.5圈虛擬電容陣列,即與信號流方向垂直的外部虛擬電容的列數Mdx≥1.5,與信號流方向平行的外部虛擬電容的行數Mdy≥1.5。所述內部電容陣列是針對電路中若干類電容的版圖,特別地,在圖3中是指電容Cs1、Cs2、Cf1、Cf2的版圖。因此,在有限的版圖面積下,單位電容尺寸和虛擬電容面積確定了電容陣列列數的最大值M。版圖面積越小,那么電容最大列數M越小;同理,單位電容尺寸越大,在版圖面積一定的情況下,電容最大列數M越小,對電容陣列版圖布局要求就越高。單邊內部電容陣列版圖列數的最大值Mh等於電容陣列列數最大值M的一半減去虛擬電容的列數Mdx,即Mh=M/2-Mdx,Mh取整數,Mdx≥1.5。該實施例中,虛擬電容的列數取1.5列,此時,例如,當版圖上最多能布局17列電容陣列時,單邊內部電容陣列版圖列數最大值Mh就等於7。當然,其他實施方式中,所述虛擬電容的列數也可以是大於1.5的其他值。

接下來將描述步驟721中如何確定電容Cs1在單邊內部電容陣列版圖布局中的最小列數M1。如前所述,步驟71中所述的單位電容的布線方法保證了單位電容環境的一致性。同時也限制了版圖上每一列電容可以與外界連線的信號個數最多只能是兩個。MDAC結構中,電容Cs1由x1個單位電容組成,每個單位電容在放大相時根據比較器的輸出碼D控制選擇開關是否導通以連線基準電平VR,意味著構成電容Cs1的x1個單位電容的下極板連線著不同的信號(也就是說,電容Cs1的單位電容具有不同的電路連線方式),因此電容Cs1在單邊內部電容陣列版圖布局中的最小列數M1=x1/2。例如,假設當電容Cs1的個數x1等於7時,電容Cs1在單邊內部電容陣列版圖布局中的最小列數M1則等於3.5。

接下來描述步驟722中如何確定電容Cs2在單邊內部電容陣列版圖布局中的列數M2、電容Cf1在單邊內部電容陣列版圖布局中的列數M3以及電容Cf2在單邊內部電容陣列版圖布局中的列數M4。MDAC結構中,電容Cs2由x2個單位電容構成,每個單位電容在放大相時的電路連線方式完全一致,因此,將這些單位電容排成一列或多列都可以,甚至,如果電容Cs1在單邊內部電容陣列版圖布局中的最小列數M1為0.5的奇數倍時,電容Cs2中的部分單位電容可以與Cs1中的某個單位電容共用一列。電容Cf1和Cf2的版圖布局與電容Cs2同理。

因此,電容陣列布局不是唯一的,但必須滿足兩個原則。第一,電容Cs2在單邊內部電容陣列版圖布局中的列數M2,電容Cf1在單邊內部電容陣列版圖布局中的列數M3,電容Cf2在單邊內部電容陣列版圖布局中的列數M4,與電容Cs1在單邊內部電容陣列版圖布局中的最小列數M1小於或等於單邊內部電容陣列版圖列數的最大值Mh;第二,每一列電容最多只能含有兩種不同電路連線方式的電容。電容的電路連線方式解釋如下:請參考圖3所示的電容陣列Cf1、Cf2和Cs2,這三類電容的上極板都連線殘差運算放大器302的輸入端,而電容的下極板具有不同的電路連線方式,具體為:電容Cf1的下極板在採樣相時鐘信號Ф1控制時與輸入信號Vi相連、在反饋相時鐘信號Ф2控制時其下極板與殘差運算放大器302的輸出端Vres相連;電容Cf2的下極板在採樣相時鐘信號Ф1以及在反饋相時鐘信號Ф2控制下都與Vres相連;電容Cs2的下極板在採樣相時鐘信號Ф1控制時與輸入信號Vi相連、以及在反饋相時鐘信號Ф2控制時與交流地相連。也就是說,電容Cf1、Cf2以及Cs2的電路連線方式均不同,此時,可以將電容Cf1、Cf2、Cs2中的任意兩類電容放在同一列,而不能同時將Cf1、Cf2、Cs2放在同一列。

在單邊內部電容陣列版圖列數最大值Mh充裕的情況下,可以對電容陣列的列數M和行數N進行折衷。如果電容Cs2在單邊內部電容陣列版圖布局中列數M2越小,而構成這種電容的單元電容個數x2比較大,則整個電容陣列版圖行數N會增加。所以,在單邊內部電容陣列版圖列數最大值Mh比較充裕的情況下,可以讓電容Cs2在單邊內部電容陣列版圖布局中列數M2適當增加,以降低整個版圖的高度N。同理,對於電容Cf1在單邊內部電容陣列版圖布局中的列數M3以及電容Cf2在單邊內部電容陣列版圖布局中的列數M4要求也是如此。然而,如果單邊內部電容陣列版圖列數最大值Mh非常緊張,只有增加電容陣列版圖行數N。

接下來將描述步驟723。在電容陣列列數M受限的情況下,步驟720、步驟721及步驟722分別確定了每種類型電容在單邊內部電容陣列版圖布局中的列數,步驟72中電容陣列布局剩下的工作就是如何對每種類型的電容進行布局了。在這一步驟中,電容布局的考慮是要方便外部版圖布線。特別地,流水線模數轉換器中,為了方便外部版圖布線,單邊內部電容陣列布局如圖9所示,其中電容Cs2放在版圖中心,為M2列,電容Cf1和電容Cf2放在單邊內部電容陣列版圖最外面方便輸出連線,且分別為M3列和M4列,電容Cs1則放在Cf1、Cf2與Cs2中間,為M1列。在單邊內部電容陣列內部空白的地方則用虛擬電容補齊。當然,在內部電容陣列外圍還應該打上至少1.5圈虛擬電容(圖9中未示)。

例如,當版圖上最多能布局17列電容陣列,電容Cs1的個數x1等於7,電容Cs2的單位電容個數x2等於7,電容Cf1的單位電容個數x3等於2,電容Cf2的單位電容個數x4等於2時,由前所述,單邊電容陣列版圖列數最大值Mh就等於7,電容Cs1在單邊內部電容陣列版圖布局中的最小列數M1等於3.5,因此,剩下的用於連線電容Cs2、Cf1和Cf2的列數M2+M3+M4應該小於或等於Mh-M1,為3.5。該電容陣列版圖布局如圖10所示。電容Cs2位於單邊內部電容陣列版圖中心,電容Cf1和電容Cf2位於單邊內部電容陣列版圖外側,電容Cs1放在Cf1、Cf2與Cs2中間。這裡電容陣列外圍的1.5圈虛擬電容沒有在圖中展示出來。圖10中,標號100表示電容Cf1的單位電容,標號200表示電容Cf2的單位電容,標號300表示電容Cs1的單位電容,標號400表示電容Cs2的單位電容。

電容Cf1排列成3.5列,每兩個單位電容排成一列。為了充分利用版圖的橫向面積,而儘量不增加版圖的高度N,將電容Cs2的7個電容分成兩列進行布局。由於版圖列數M受限,電容Cf1和電容Cf2放置成一列,其餘空白的地方用虛擬電容補齊。這樣,可以看到單邊內部電容陣列版圖列數是7,行數等於4,算上電容外圍的1.5圈虛擬電容,單邊電容陣列版圖列數是8.5,行數等於7。

當電容布局完成後(即步驟72執行完成後),就可以進行步驟73中描述的電容陣列布線。如圖11所示,由於步驟71中的單位電容布線方式的確定,使得單位電容之間寄生電容的不匹配來源主要就是上極板連線與下極板連線之間的寄生電容。在這裡,也就是上極板連線金屬鋁線2和下極板連線金屬鋁線1之間的寄生電容。圖11中的寄生電容Cpl是附加於電容91的寄生電容,主要來源是電容91上極板連線和下極板連線之間的寄生電容。寄生電容Cp2是附加在另外一個單位電容的寄生電容,所述單位電容的上極板連線與電容91的上極板相連,下極板與右側金屬鋁線1相連。寄生電容與連線間距、連線並行長度L有關。連線間距越小,連線並行長度L越大,寄生電容Cp就越大。由於單位電容布線方式保證了上下極板連線的間距相同,因此,要使每個單位電容的寄生電容Cp一致,關鍵就是保證單位電容上下極板連線的並行長度L一致。

圖12是圖10對應的電容陣列布線示意圖。為了方便說明,結合圖12介紹電容陣列布線方法。流水線模數轉換器的MDAC結構中,電容Cs1、Cs2、Cf1和Cf2的上極板都是連線到運算放大器的輸入端,因此這些電容的上極板都通過金屬鋁線2沿著信號流方向與運算放大器的輸入端連線。而所有單位電容的下極板連線都沿著信號流的反方向與外部連線。由前面可知,版圖上電容Cs1在每一列最多包含兩個不同下極板連線的單位電容,因此,當外部信號與電容Cs1的下極板相連線時,下極板的布線分為兩種情況。當這一列電容有兩個不同下極板連線的單位電容時,如圖12中的M12、M13、M14列電容,只有一條金屬鋁線1通過打孔連線到下極板。當這一列電容只有一種下極板連線的電容,如圖12中的M11列,則有兩條金屬鋁線1通過打孔連線到下極板,這樣每個單位電容的上極板連線與下極板連線並行的長度L都為兩個單位電容的長度。

電容Cs2在放大相時的電路特性連線方式完全一致,在版圖布局上也被放置成一列或多列。為了保證電容Cs2的上極板連線與下極板連線並行的長度L都為兩個單位電容的長度,同理,當這一列電容全都是Cs2的單位電容時,如圖12中的M21和M22列,兩條金屬鋁線1均通過打孔連線到下極板。當電容Cs2中的某個單位電容與其他類型的某個單位電容共用一列時,只有一條金屬鋁線1通過打孔連線到下極板。

電容Cf1和Cf2的布線方法類似,目的都是保證單位電容上下極板連線的並行長度L為兩個單位電容的長度。圖12中,電容Cf1和電容Cf2共用一列,因此,每個電容的下極板都只與一條金屬鋁線1相連。在虛擬電容的布線中,需要讓其上極板和下極板都連線地(圖未示)。

完成步驟72中的電容陣列布局和步驟73中的電容陣列布線後,隨即進行步驟74(即寄生參數提取步驟)。寄生參數提取的目的是驗證並確定電容陣列的匹配精度。利用ASSURA等工具進行版圖驗證並提取寄生參數,電容陣列中的每個單位電容的寄生參數都可以通過工具顯示出來,據此可以分析每個單元電容的寄生參數和電容陣列的匹配精度是否滿足要求。

隨著MOS工藝的進步,寄生電容的影響越來越嚴重,寄生電容不匹配逐漸成為電容不匹配的主要因素,上述電容陣列及其版圖設計方法的主要創新點是消除了寄生電容的不匹配,以產生匹配的電容陣列,因此該發明完全適用於先進工藝下的電容陣列版圖設計和金屬-金屬電容陣列版圖設計。

榮譽表彰