《用於在高性能互連中定中心的方法、設備、系統》是英特爾公司於2015年11月28日申請的專利,該專利公布號為CN107005231B,專利公布日為2021年6月8日,發明人是M.瓦格、吳佐國、V.伊耶爾、G.S.帕斯達斯特、T.A.欣克、D.M.李、N.R.蘭卡。

基本介紹

- 中文名:用於在高性能互連中定中心的方法、設備、系統

- 授權公告號:CN107005231B

- 授權公告日:2021年6月8日

- 申請號:2015800645540

- 申請日:2015.11.28

- 專利權人:英特爾公司

- 地址:美國加利福尼亞州

- 發明人:M.瓦格; 吳佐國; V.伊耶爾; G.S.帕斯達斯特; T.A.欣克; D.M.李; N.R.蘭卡

- Int. Cl.:H03K5/26(2006.01)I

- 專利代理機構:中國專利代理(香港)有限公司72001

- 代理人:徐紅燕; 張濤

- 優先權:14/583139 2014.12.25 US

- PCT進入國家階段日:2017.05.26

- PCT申請數據:PCT/US2015/062855 2015.11.28

- PCT公布數據:WO2016/105862 EN 2016.06.30

對比檔案,專利摘要,

對比檔案

CN 103378827 A,2013.10.30; CN 102109604 A,2011.06.29; EP 2775620 A2,2014.09.10; CN 103412644 A,2013.11.27; CN 103718182 A,2014.04.09; US 2009016476 A1,2009.01.15; US 7275193 B1,2007.09.25

胡建國.高性能微處理器的驗證技術研究.《中國優秀碩士學位論文全文資料庫 信息科技輯》.2006,第I137-24頁.; H. Harrer 等.High-speed interconnect and packaging design of the IBM System z9 processor cage.《IBM Journal of Research and Development》.2007,第37-52頁.

專利摘要

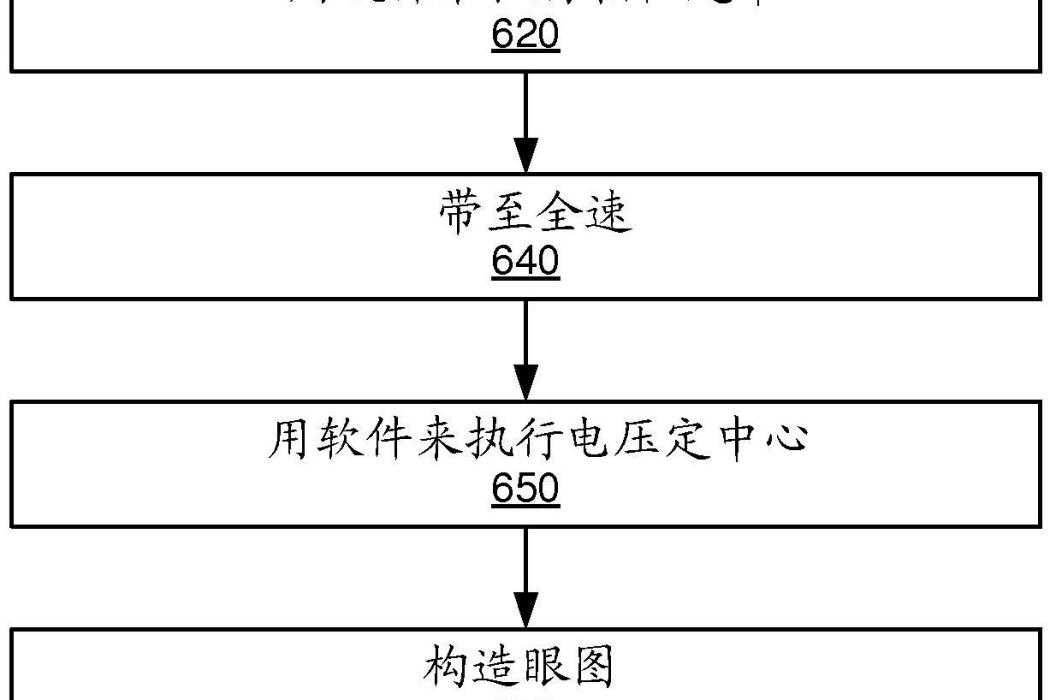

在示例中,公開了一種用於在高性能互連(HPI)中定中心的系統和方法。當互連被從休眠狀態上電時,可能必須對時鐘信號“定中心”以確保數據在正確的時間被讀取。可以使用多階段方法,其中第一階段包括用以識別最優參考電壓的參考電壓掃描。第二階段包括用以識別最優相位的相位掃描。第三掃描包括二維“眼圖”階段,其中測試從前兩次掃描導出的二維眼圖內的多個值。在每種情況下,最優值是導致跨多個通道的最少位錯誤的值。在一個示例中,第二和第三階段是用軟體執行的,並且可以包括測試“受害者”通道,其中鄰近的“侵略者”通道具有互補的位模式。