《獲得垂直型溝道高壓超級結半導體器件的方法》是上海華虹NEC電子有限公司於2009年5月26日申請的發明專利,該專利申請號為200910057313X,公布號為CN101901767A,專利公布日為2010年12月01日,發明人是肖勝安。

2017年12月11日,《獲得垂直型溝道高壓超級結半導體器件的方法》獲得第十九屆中國專利優秀獎。

《獲得垂直型溝道高壓超級結半導體器件的方法》公開了一種獲得垂直型溝道高壓超級結半導體器件的方法,步驟一、在N+基板上進行第一次N型外延成長;步驟二、刻蝕所述N型外延層,在N型外延層上形成一定高寬比的溝槽穿通到N+基板上;步驟三、在所述溝槽中填入P型外延層;步驟四、利用化學機械研磨得到平坦的N型柱子和P型柱子交替出現的結構;步驟五、在步驟四形成的N型柱子和P型柱子交替出現的結構上進行第二次N型外延成長,然後重複實施步驟二至四得到更高P型溝槽高寬比的平坦的N型柱子和P型柱子交替出現的結構,直到N型外延層的厚度達到器件阻擋電壓的要求。本發明能夠在工藝難度不增大的條件下有效減少P型柱子占比,降低比抵抗電阻。

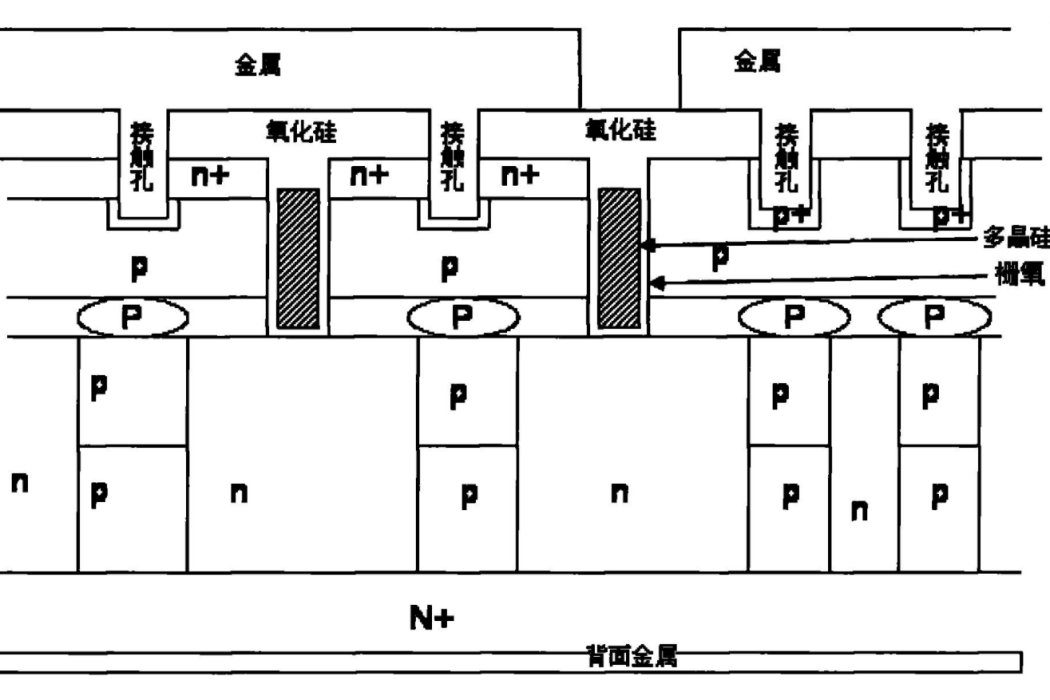

(概述圖為《獲得垂直型溝道高壓超級結半導體器件的方法》的摘要附圖)

基本介紹

- 中文名:獲得垂直型溝道高壓超級結半導體器件的方法

- 公布號:CN101901767A

- 公布日:2010年12月1日

- 申請號:200910057313X

- 申請日:2009年5月26日

- 申請人:上海華虹NEC電子有限公司

- 地址:上海市浦東新區川橋路1188號

- 發明人:肖勝安

- 代理機構:上海浦一智慧財產權代理有限公司

- 代理人:戴廣志

- Int.Cl.:H01L21/337(2006.01)I

- 類別:發明專利

專利背景,發明內容,專利目的,技術方案,改善效果,附圖說明,技術領域,權利要求,實施方式,榮譽表彰,

專利背景

超級結MOSFET(metal—oxide—semiconductorfield—effecttransistor金屬氧化物半導體場效應電晶體)採用新的耐壓層結構,利用一系列交替排列的P型和N型半導體薄層(半導體薄層或稱為柱子),在截止狀態且較低電壓下就將P型和N型區耗盡,實現電荷相互補償;從而使N型區在高摻雜濃度下實現高的擊穿電壓,同時獲得低導通電阻,打破傳統功率MOSFET理論極限。因此這種新的耐壓層結構在高壓器件中受到越來越多的重視。

所述新的耐壓層結構製作方法可分為兩種:一是利用多次外延成長—光刻—注入來獲得交替的P型和N型摻雜區;二是在N型矽外延層上開溝槽,向溝槽中填入P型多晶,或傾斜注入P型雜質,或填入P型外延。第一種方法不僅工藝複雜,成本很高,而且實現難度大;例如一般600伏的器件需要5—7次外延成長—光刻—注入,經過多次外延生長後,光刻需要的對準標記往往因為變形沒法識別,這時就需要在2—3次外延成長後通過額外的工藝來作出新的對準標記。第二種方法中,傾斜注入由於穩定性和重複性差不能用入批量生產,所需雜質濃度的P型多晶矽迄今為止未能在工藝上實現,因此P型外延填入工藝受到關注。

在P型外延填入工藝中,深溝槽刻蝕和外延填入是關鍵:所述寬溝槽的高寬比越大(一般600伏器件中,溝槽深度約45—50微米,寬度約3—5微米,高寬比約9—16)就能使P型柱子的占比〔即器件單元中,P型柱子的面積除以(P型柱子的面積+N型柱子的面積)〕越小,器件導通時電流可流通的面積(N型柱子面積)越大,器件的比抵抗電阻就越小。但是刻蝕具有很高高寬比(如大於6:1)的溝槽在工藝上難度很大,往這樣高高寬比的溝槽中填入外延層也有加工困難。此外,通過已有的P型外延填入工藝得到的器件,還主要是平面型器件(參見圖1)。與垂直型器件相比,平面型器件的單元面積大,因此平面型器件的比抵抗電阻相對較大。

發明內容

專利目的

《獲得垂直型溝道高壓超級結半導體器件的方法》要解決的技術問題是提供一種獲得垂直型溝道高壓超級結半導體器件的方法,能夠減少P型柱子占比,降低比抵抗電阻。

技術方案

為解決上述技術問題,《獲得垂直型溝道高壓超級結半導體器件的方法》的獲得垂直型溝道高壓超級結半導體器件的方法是採用如下技術方案實現的:

步驟一、在N+基板上進行第一次N型外延成長,並在N型外延層上形成一層介質膜;

步驟二、刻蝕所述N型外延層,在N型外延層上形成一定高寬比的溝槽穿通到N+基板上;

步驟三、在所述溝槽中填入P型外延層;

步驟四、利用化學機械研磨得到平坦的N型柱子和P型柱子交替出現的結構;

步驟五、在步驟四形成的N型柱子和P型柱子交替出現的結構上進行第二次N型外延成長,然後重複實施步驟二至四得到高於前次P型溝槽高寬比的平坦的N型柱子和P型柱子交替出現的結構,直到N型外延層的厚度達到器件阻擋電壓的要求。

《獲得垂直型溝道高壓超級結半導體器件的方法》的獲得垂直型溝道高壓超級結半導體器件的方法採用的另一種技術方案是,包括如下工藝步驟:

步驟一、在P+基板上進行第一次P型外延成長,並在P型外延層上形成一層介質膜;

步驟二、光刻刻蝕所述P型外延層,在P型外延層上形成一定高寬比的溝槽穿通到P+基板上;

步驟三、在所述溝槽中填入N型外延層;

步驟四、利用化學機械研磨得到平坦的P型柱子和N型柱子交替出現的結構;

步驟五、在步驟四形成的P型柱子和N型柱子交替出現的結構上進行第二次P型外延成長,然後重複實施步驟二至四得到高於前次N型溝槽高寬比的平坦的P型柱子和N型柱子交替出現的結構,直到P型外延層的厚度達到器件阻擋電壓的要求。

改善效果

採用《獲得垂直型溝道高壓超級結半導體器件的方法》的方法,在工藝難度不增大的條件下,利用多次不同能量的P阱注入減小熱過程,以減小P型柱子的擴散,使交替排列的P型區和N型區半導體薄層中P型區的占比減小,以得到更低的比抵抗電阻,並獲得更高高寬比的P型柱子。

在接觸孔打開後,進行高能量離子注入,能實現深溝槽P型雜質與P阱的接通。

附圖說明

圖1是截至2009年5月前已有的P外延填入溝槽的超級結MOSFET(平面型)結構圖;

圖2是採用《獲得垂直型溝道高壓超級結半導體器件的方法》的方法溝槽刻蝕完成後示意圖;

圖3是採用《獲得垂直型溝道高壓超級結半導體器件的方法》的方法P型外延填充溝槽完成後示意圖;

圖4是採用《獲得垂直型溝道高壓超級結半導體器件的方法》的方法外延層化學機械研磨完成後示意圖;

圖5是重複圖2—4的工藝方法完成後示意圖;

圖6是採用《獲得垂直型溝道高壓超級結半導體器件的方法》的方法溝槽工藝,P阱注入,N+源注入,接觸孔工藝,深P型注入完成後示意圖;

圖7是採用《獲得垂直型溝道高壓超級結半導體器件的方法》的方法P+注入完成後示意圖;

圖8是採用《獲得垂直型溝道高壓超級結半導體器件的方法》的方法表面金屬光刻/刻蝕,背面金屬工藝完成後器件結構示意圖。

技術領域

《獲得垂直型溝道高壓超級結半導體器件的方法》涉及一種半導體積體電路的製造工藝方法,特別是涉及一種獲得垂直型溝道高壓超級結半導體器件的方法。

權利要求

1.一種獲得垂直型溝道高壓超級結半導體器件的方法,其特徵在於,包括如下工藝步驟:

步驟一、在N+基板上進行第一次N型外延成長,並在N型外延層上形成一層介質膜;

步驟二、光刻刻蝕所述N型外延層,在N型外延層上形成一定高寬比的溝槽穿通到N+基板上;

步驟三、在所述溝槽中填入P型外延層;

步驟四、利用化學機械研磨得到平坦的N型柱子和P型柱子交替出現的結構;

步驟五、在步驟四形成的N型柱子和P型柱子交替出現的結構上進行第二次N型外延成長,然後重複實施步驟二至四得到高於前次P型溝槽高寬比的平坦的N型柱子和P型柱子交替出現的結構,直到N型外延層的厚度達到器件阻擋電壓的要求。

2.如權利要求1所述的方法,其特徵在於:後面一次在N型外延層上形成的溝槽的底部要接觸到前一次溝槽的頂部。

3.如權利要求1或2所述的方法,其特徵在於:還包括如下步驟:

步驟六、再成長器件溝道區所需要的N型外延;

步驟七、通過光刻刻蝕得到用於製作器件溝道的溝槽;

步驟八、通過熱氧化在所述製作器件溝道的溝槽中形成柵氧,然後再填入N型多晶矽,通過回刻或化學機械研磨得到平坦的多晶矽填好的溝槽;

步驟九、注入P型雜質形成器件的阱;

步驟十、進行N+源的刻蝕和離子注入,形成N+源區;

步驟十一、進行層間膜成長;

步驟十二、進行接觸孔光刻刻蝕;

步驟十三、利用高能量P型注入實現溝槽P型雜質與P阱的接通;再通過P+注入實現P+歐姆接觸;

步驟十四、表面金屬成長—光刻—刻蝕形成源極,多晶矽柵的走線;

步驟十五、矽片減薄—背面金屬化,形成漏極。

4.如權利要求3所述的方法,其特徵在於:步驟九在形成器件的阱過程中採用多次不同能量的P型雜質注入的方式,並配合一定的熱過程。

5.如權利要求1或2所述的方法,其特徵在於:重複實施步驟二時,光刻既可以使用與前次光刻同樣的掩膜版,也可以根據工藝需要採用新的掩膜版。

6.一種獲得垂直型溝道高壓超級結半導體器件的方法,其特徵在於,包括如下工藝步驟:

步驟一、在P+基板上進行第一次P型外延成長,並在P型外延層上形成一層介質膜;

步驟二、光刻刻蝕所述P型外延層,在P型外延層上形成一定高寬比的溝槽穿通到P+基板上;

步驟三、在所述溝槽中填入N型外延層;

步驟四、利用化學機械研磨得到平坦的P型柱子和N型柱子交替出現的結構;

步驟五、在步驟四形成的P型柱子和N型柱子交替出現的結構上進行第二次P型外延成長,然後重複實施步驟二至四得到高於前次N型溝槽高寬比的平坦的P型柱子和N型柱子交替出現的結構,直到P型外延層的厚度達到器件阻擋電壓的要求。

7.如權利要求6所述的方法,其特徵在於:後面一次在P型外延層上形成的溝槽的底部要接觸到前一次溝槽的頂部。

實施方式

參見圖2—8所示,《獲得垂直型溝道高壓超級結半導體器件的方法》獲得垂直型溝道高壓超級結半導體器件的方法包括如下工藝步驟:

步驟一、在N+基板上進行第一次N型外延成長,並在N型外延層上形成一層介質膜。

步驟二、刻蝕所述N型外延層,在N型外延層上形成一定高寬比的溝槽穿通到N+基板上(參見圖2所示)。刻蝕的方法可以採用已知的各種截至2009年5月前的已有技術。所述一定高寬比的溝槽可以是高寬比大於或等於4∶1的溝槽。

步驟三、參見圖3所示,在所述溝槽中填入P型外延層。

步驟四、利用化學機械研磨得到平坦的N型柱子和P型柱子交替出現的結構(結合圖4所示)。

步驟五、在步驟四形成的N型柱子和P型柱子交替出現的結構上進行第二次N型外延成長,然後重複實施步驟二至四得到更高(當第一次刻蝕的溝槽高寬比為4∶1時,那么經過第二次刻蝕後的溝槽高寬比將變為8∶1)P型溝槽高寬比的平坦的N型柱子和P型柱子交替出現的結構,直到N型外延層的厚度達到器件阻擋電壓的要求。

在重複實施上述步驟二至五的過程中,後面一次在N型外延層上形成的溝槽的底部要接觸到前一次溝槽的頂部。圖5是重複一次步驟二至四後得到的結構。由於在以上工藝過程中每次光刻刻蝕可以通過刻蝕製作新的對準標記,不會出現因多次實施外延—光刻—離子注入工藝使對準標記變形的問題。

在重複實施上述步驟二至五的過程中,重複光刻既可以使用與前次同樣的掩膜版,也可以根據工藝需要採用新的掩膜版。例如如果前次的對準標記在下次外延成長後出現變形不能適用,可採用新掩膜版放入新的對準標記。

上述步驟二中所述的一定高寬比,要根據器件的要求和設備的加工能力來選定,按照器件要求的溝槽寬度,選擇單次刻蝕和外延層成長工藝能完成的最大的溝槽深度,以減小完成目標N型柱子和P型柱子所需要的步驟一到步驟四的重複次數,節約成本。例如對於一個特定器件,如單元PITCH15微米,溝槽寬3微米,溝槽深50微米的設計,可以通過兩次步驟一到步驟四的重複,每次實現溝槽寬3微米,溝槽深25微米的相關工藝來實現,也可以通過四次步驟一到步驟四的重複,每次實現溝槽寬3微米,溝槽深12.5微米的相關工藝來完成,在工藝能力能達到的情況下前者(兩次步驟一到步驟四的重複)具有成本低的優點。

步驟六、再成長器件溝道區所需要的N型外延。

步驟七、通過光刻刻蝕得到用於製作器件溝道的溝槽。

步驟八、通過熱氧化在所述製作器件溝道的溝槽中形成柵氧,然後再填入N型多晶矽,通過回刻或化學機械研磨得到平坦的多晶矽填好的溝槽。

步驟九、注入P型雜質形成器件的阱(根據不同器件設計的需求,有時是全矽片注入,有時是在終端區以外的區域注入)。在形成器件的阱過程中採用多次不同能量的P型雜質注入的方式,以減少得到均勻的P阱所需要的熱過程,從而減小P型柱子的擴散,使交替排列的P型和N型半導體薄層(即P型柱子和N型柱子)中P型的占比減小。

步驟十、進行N+源的刻蝕和離子注入,形成N+源區。

步驟十一、進行層間膜成長(矽片全面成長)。

步驟十二、進行接觸孔(Cont)光刻刻蝕。

步驟十三、參見圖6所示,利用高能量P型注入,實現深溝槽P型雜質與P阱的接通;對於600伏的MOSFET,步驟六生長的外延厚度一般為3—4微米,步驟七形成的溝槽深度一般為2.5—3微米,步驟九和隨後的熱過程形成的P阱深度約2微米,為使P型柱子與P阱通過該次注入實現連通,注入的硼的能量大約為1000—1500千電子伏特。結合圖7所示,再通過P+注入(垂直或傾斜)實現P+歐姆接觸。

步驟十四、表面金屬成長—光刻—刻蝕,形成源極,多晶矽柵的走線。

步驟十五、矽片減薄—背面金屬化,形成漏極,參見圖8所示。

在上面所述的方法中,如果將所述P型半導體薄層區和N型半導體薄層區進行位置互換,則產生的技術效果不變。

在《獲得垂直型溝道高壓超級結半導體器件的方法》的上述實施方式中,利用多次外延成長—溝槽刻蝕—P型外延填入—P型外延化學機械研磨工藝,獲得更高高寬比的P型柱子;再進行外延成長—導通溝道用溝槽刻蝕—多次不同能量P阱注入—N+注入—層間膜成長—接觸孔圖形化—P型高能量注入—P+接觸孔注入—表面及背面金屬化等工藝步驟得到低比導通電阻的垂直型溝道高壓超級結MOSFET器件結構,具體結構如圖8所示。

榮譽表彰

2017年12月11日,《獲得垂直型溝道高壓超級結半導體器件的方法》獲得第十九屆中國專利優秀獎。