《光子集成晶片匹配電路的三維封裝裝置》是中國科學院半導體研究所於2012年9月14日申請的發明專利,該專利申請號為2012103422843,公布號為CN102856302A,公布日為2013年1月2日,發明人是祝寧華、王佳勝、劉建國、劉宇。

《光子集成晶片匹配電路的三維封裝裝置》公開了一種光子集成晶片匹配電路的三維封裝裝置,包括:一第一載體基片;一第一微波傳輸線陣列,蒸鍍在該第一載體基片的上表面,用於給光子集成晶片提供偏置電壓和高頻調製信號;一第二載體基片,與該第一載體基片垂直或成一定角度,形成三維立體結構;一第二微波傳輸線陣列,蒸鍍在該第二載體基片的下表面,且與該第一微波傳輸線陣列的電極相匹配並進行焊接或燒結;一電極陣列,蒸鍍在該第二載體基片的一個側面或相對的兩個側面;以及一微波電路。該發明克服光子集成晶片陣列封裝時因陣列晶片間距限制導致的匹配電路尺寸受限的問題,突破微波電路的傳統設計只在二維平面的局限,增加電路設計的維度,為微波電路的設計預留空間。

2021年6月24日,《光子集成晶片匹配電路的三維封裝裝置》獲得第二十二屆中國專利優秀獎。

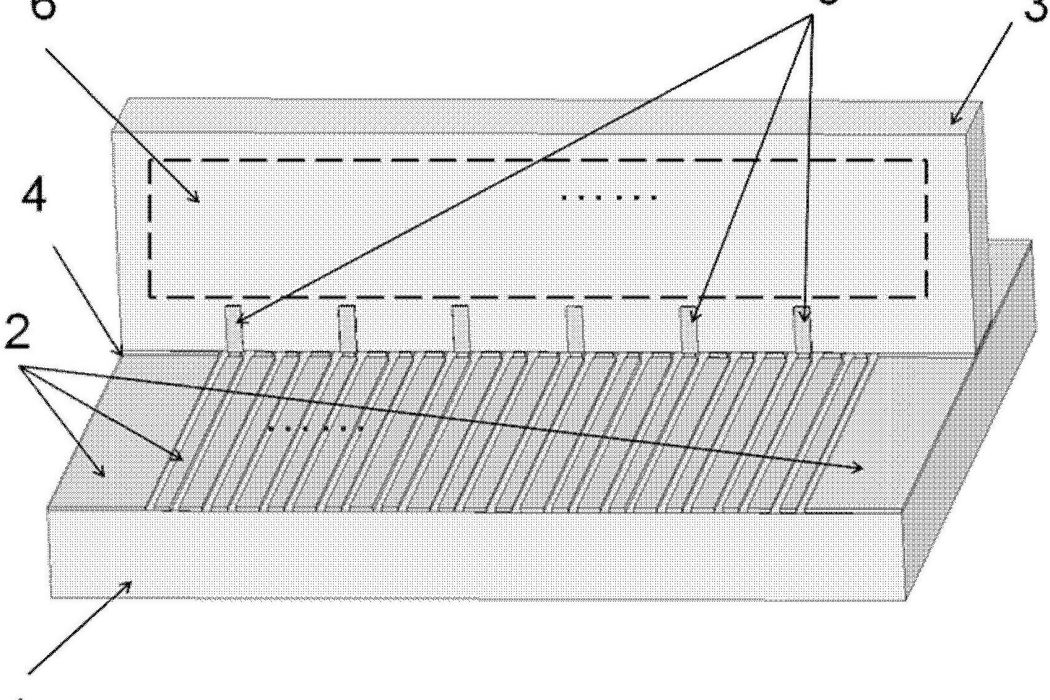

(概述圖為《光子集成晶片匹配電路的三維封裝裝置》摘要附圖)

基本介紹

- 中文名:光子集成晶片匹配電路的三維封裝裝置

- 申請日:2012年9月14日

- 申請號:2012103422843

- 申請公布日:2013年1月2日

- 申請公布號:CN102856302A

- 申請人:中國科學院半導體研究所

- 地址:北京市海淀區清華東路甲35號

- 發明人:祝寧華、王佳勝、劉建國、劉宇

- 類別:發明專利

- Int. Cl.:H01L23/58(2006.01)I; H01L23/66(2006.01)I; H01L23/367(2006.01)I

- 專利代理機構:中科專利商標代理有限責任公司

- 代理人:任岩

專利背景,發明內容,專利目的,技術方案,有益效果,附圖說明,技術領域,權利要求,實施方式,專利榮譽,

專利背景

截至2012年9月,由分立光電子器件構建的光網路設備難以適應飛速發展的光纖通信網路,光子集成晶片(PIC)是實現大容量、低功耗光網路所必須依賴的技術。為了將外部微波信號有效地載入到光子集成晶片上,要求過渡熱沉有高效率低反射低損耗的阻抗匹配微波電路。

與分立器件顯著不同,超高集成度使集成器件尺度縮小到微納量級,這對器件的研製和封裝提出了更為嚴格的要求。當前分立器件封裝所經常採用的微波波導的電路設計在陣列封裝中並不適用。如果採用單路封裝常用的共面波導傳輸線或者微帶傳輸線電路,在傳輸線末端並聯匹配電阻,則匹配電阻由於多路集成器件的尺寸限制難以加工。如果採用金絲將電極引出,由於器件尺寸限制,又會出現因為金絲過長以及直徑過細而導致明顯的電感效應,引入較多寄生參數,影響整個陣列的高頻性能。

此外,由於超高集成度造成的管芯陣列散熱問題,也可通過《光子集成晶片匹配電路的三維封裝裝置》達到改善。

發明內容

專利目的

《光子集成晶片匹配電路的三維封裝裝置》的主要目的在於提供一種光子集成晶片匹配電路的三維封裝裝置,以克服光子集成晶片陣列封裝時因陣列晶片間距限制導致的匹配電路尺寸受限的問題,突破微波電路的傳統設計只在二維平面的局限,增加電路設計的維度,為微波電路的設計預留空間。

技術方案

《光子集成晶片匹配電路的三維封裝裝置》提供了一種光子集成晶片匹配電路的三維封裝裝置,包括:一第一載體基片1;一第一微波傳輸線陣列2,蒸鍍在該第一載體基片1的上表面,用於給光子集成晶片提供偏置電壓和高頻調製信號;一第二載體基片3,與該第一載體基片1垂直或成一定角度,形成三維立體結構;一第二微波傳輸線陣列4,蒸鍍在該第二載體基片3的下表面,且與該第一微波傳輸線陣列2的電極相匹配並進行焊接或燒結;一電極陣列5,蒸鍍在該第二載體基片3的一個側面或相對的兩個側面;以及一微波電路6。

上述方案中,其中該第一載體基片1和該第二載體基片3採用的材料是氮化鋁、氮化鈹、氧化鋁、金剛石、氧化鈹或碳化矽。

上述方案中,其中該第一微波傳輸線陣列2和該第二微波傳輸線陣列4中的傳輸線單元採用的是共面波導或微帶傳輸線。

上述方案中,其中該電極陣列5的邊緣幾何尺寸與該第二微波傳輸線陣列4中的信號電極陣列相連線並過渡。

上述方案中,其中該微波電路6是阻抗匹配電路、直流偏置電路或其他微波封裝電路。

有益效果

1、《光子集成晶片匹配電路的三維封裝裝置》提供的這種光子集成晶片匹配電路的三維封裝裝置,克服了光子集成晶片陣列封裝時因陣列晶片間距限制導致的匹配電路尺寸受限的問題,突破了微波電路的傳統設計只在二維平面的局限,增加了電路設計的維度,為微波電路的設計預留了極大的空間。

2、《光子集成晶片匹配電路的三維封裝裝置》提供的這種光子集成晶片匹配電路的三維封裝裝置,既減少了器件模組的反射參量,又減少了金絲數量和長度,提高了微波信號的調製效率,實現了光子集成晶片的阻抗匹配,適用於多路並行雷射器、電吸收調製器等多種器件集成結構的封裝。

3、《光子集成晶片匹配電路的三維封裝裝置》提供的這種光子集成晶片匹配電路的三維封裝裝置,光子集成陣列晶片的過渡熱沉散熱面積擴大,散熱能力大大增強。

附圖說明

圖1是《光子集成晶片匹配電路的三維封裝裝置》提供的光子集成晶片匹配電路的三維封裝裝置的結構示意圖。

圖2-1,圖2-2,圖2-3是《光子集成晶片匹配電路的三維封裝裝置》一種光子集成晶片匹配電路的三維封裝裝置的一個實施例示意圖,是一種電吸收調製雷射器陣列封裝的阻抗匹配電路。

圖3是該用於電吸收調製雷射器陣列封裝的阻抗匹配電路的第二載體基片3及蒸鍍在第二載體基片3表面的微波電路示意圖。

圖4是該用於電吸收調製雷射器陣列封裝的阻抗匹配電路的第一載體基片1及蒸鍍在第一載體基片1表面的微波電路示意圖。

圖5-1,圖5-2是《光子集成晶片匹配電路的三維封裝裝置》一種光子集成晶片匹配電路的三維封裝裝置的一個實施例示意圖,是一種直接調製雷射器陣列封裝的偏置電路與阻抗匹配電路。

圖6是該用於直接調製雷射器陣列封裝的偏置電路與阻抗匹配電路的第二載體基片3及蒸鍍在第二載體基片3表面的微波電路示意圖。

圖7是該用於直接調製雷射器陣列封裝的偏置電路與阻抗匹配電路的第一載體基片1及蒸鍍在第一載體基片1表面的微波電路示意圖。

技術領域

《光子集成晶片匹配電路的三維封裝裝置》屬於光電子器件領域,更具體說是光子集成晶片匹配電路的三維封裝裝置。

權利要求

1.一種光子集成晶片匹配電路的三維封裝裝置,其特徵在於,包括:一第一載體基片(1);一第一微波傳輸線陣列(2),蒸鍍在該第一載體基片(1)的上表面,用於給光子集成晶片提供偏置電壓和高頻調製信號;一第二載體基片(3),與該第一載體基片(1)垂直或成一定角度,形成三維立體結構;一第二微波傳輸線陣列(4),蒸鍍在該第二載體基片(3)的下表面,且與該第一微波傳輸線陣列(2)的電極相匹配並進行焊接或燒結;一電極陣列(5),蒸鍍在該第二載體基片(3)的一個側面或相對的兩個側面,且該電極陣列(5)的邊緣幾何尺寸與該第二微波傳輸線陣列(4)中的信號電極陣列相連線並過渡,實現第二微波傳輸線陣列(4)與電極陣列(5)之間的電連線;以及一微波電路(6)。

2.如權利要求1所述的光子集成晶片匹配電路的三維封裝裝置,其特徵在於,其中該第一載體基片(1)和該第二載體基片(3)採用的材料是氮化鋁、氮化鈹、氧化鋁、金剛石、氧化鈹或碳化矽。

3.如權利要求1所述的光子集成晶片匹配電路的三維封裝裝置,其特徵在於,其中該第一微波傳輸線陣列(2)和該第二微波傳輸線陣列(4)中的傳輸線單元採用的是共面波導或微帶傳輸線。

4.如權利要求1所述的光子集成晶片匹配電路的三維封裝裝置,其特徵在於,其中該微波電路(6)是阻抗匹配電路、直流偏置電路或其他微波封裝電路。

實施方式

如圖1所示,圖1是《光子集成晶片匹配電路的三維封裝裝置》提供的光子集成晶片匹配電路的三維封裝裝置的結構示意圖,該裝置包括:一第一載體基片1;一第一微波傳輸線陣列2,蒸鍍在該第一載體基片1的上表面,用於給光子集成晶片提供偏置電壓和高頻調製信號;一第二載體基片3,與該第一載體基片1垂直或成一定角度,形成三維立體結構;一第二微波傳輸線陣列4,蒸鍍在該第二載體基片3的下表面,且與該第一微波傳輸線陣列2的電極相匹配並進行焊接或燒結;一電極陣列5,蒸鍍在該第二載體基片3的一個側面或相對的兩個側面;以及一微波電路6。

其中,該第一載體基片1和該第二載體基片3採用的材料是氮化鋁、氮化鈹、氧化鋁、金剛石、氧化鈹或碳化矽。該第一微波傳輸線陣列2和該第二微波傳輸線陣列4中的傳輸線單元採用的是共面波導或微帶傳輸線。該電極陣列5的邊緣幾何尺寸與該第二微波傳輸線陣列4中的信號電極陣列相連線並過渡。該微波電路6是阻抗匹配電路、直流偏置電路或其他微波封裝電路。

參閱圖2~圖4的實施例一,《光子集成晶片匹配電路的三維封裝裝置》是一種光子集成晶片匹配電路的三維封裝裝置,實施例一是一種用於電吸收調製雷射器陣列封裝的阻抗匹配電路,其特徵在於,其中包括:

一第一載體基片1;其中該第一載體基片1可採用氮化鋁或氮化鈹或氧化鋁或金剛石或氧化鈹或碳化矽材料。

一第一微波傳輸線陣列2,該第一微波傳輸線陣列2蒸鍍在第一載體基片1的上表面,該第一微波傳輸線陣列2的每個傳輸線單元採用的是共面波導或微帶傳輸線;該第一微波傳輸線陣列2用來給光子集成晶片提供偏置電壓和高頻調製信號;在此實施例中,該第一微波傳輸線陣列2用來給光子集成晶片中的電吸收調製器陣列提供反向偏置電壓和高頻調製信號,如圖4,第一微波傳輸線陣列2採用共面波導結構,有12個傳輸線單元。

一第二載體基片3;其中該第二載體基片可採用氮化鋁或氮化鈹或氧化鋁或金剛石或氧化鈹或碳化矽材料。

一第二微波傳輸線陣列4,該第二微波傳輸線陣列4蒸鍍在第二載體基片3的下表面,該第二微波傳輸線陣列4的每個傳輸線單元採用的是共面波導或微帶傳輸線;與第一微波傳輸線陣列2的電極相匹配並進行焊接或燒結;使得第一微波傳輸線陣列2的每個信號電極單元與第二微波傳輸線陣列4的與之對應的信號電極單元接觸良好,相應的地電極也接觸良好,如圖3、圖4中的2-1與4-1,2-2與4-2。

一電極陣列5,該電極陣列5蒸鍍在第二載體基片3的一個側面或者相對的兩個側面;其邊緣幾何尺寸與第二微波傳輸線陣列4中的信號電極陣列相連線並過渡,如圖3中的5-1與4-1,5-2與4-2,在該實施例中,電極陣列5蒸鍍在第二載體基片3的兩個側面,共有12個信號電極單元。

一薄膜電阻陣列6,該薄膜電阻陣列6製作在第二載體基片3上,其材料為氮化鉭或鎳鉻合金。該薄膜電阻陣列6與電極陣列5對應連線,接觸良好,如圖例3中的6-1與5-1,6-2與5-2,該薄膜電阻陣列6中的每個電阻單元的形狀,可以是矩形扇形等規則圖形,也可以根據實際需要設計。該薄膜電阻用於與電吸收調製器陣列並聯,實現電吸收調製器的阻抗匹配。

一地電極7,該地電極7蒸鍍在第二載體基片3的一個側面或者相對的兩個側面,與電極陣列5形成共面波導結構或者微帶結構,該地電極7與薄膜電阻陣列6連線,接觸良好。如圖2所示,該地電極7蒸鍍在第二載體基片3的相對的兩個側面,與電極陣列5中的每個信號電極單元構成了共面波導結構,該地電極7與電極陣列5的每個信號電極單元之間的間隙寬度根據第二載體基片3的電學性質以及微波傳輸線特徵阻抗值確定,根據電極陣列5與地電極7構成的共面波導結構或者微帶結構的特徵阻抗值確定薄膜電阻陣列6中的每個電阻單元的阻值,滿足特徵阻抗匹配條件。該地電極7-a、7-b均與各自相對側面的信號電極序列之間做好了電隔離,防止了信號的串擾。另外,由於地電極7是在第二載體基片3的表面,金屬材料是熱的良導體,因此大大擴大了散熱面積,改善了散熱性能。

一電吸收調製雷射器晶片陣列8,在該實施例一中,該電吸收調製雷射器晶片陣列8包含12個雷射器,該電吸收調製雷射器晶片陣列8中的電吸收調製器陣列通過互連金絲組9與第一微波傳輸線陣列2的傳輸線單元對應連線。

參閱圖5~圖7的實施例二,《光子集成晶片匹配電路的三維封裝裝置》是一種光子集成晶片匹配電路的三維封裝裝置,實施例二是一種用於直接調製雷射器陣列封裝的直流偏置電路與阻抗匹配電路,其特徵在於,其中包括:

一第一載體基片1;其中該第一載體基片1可採用氮化鋁或氮化鈹或氧化鋁或金剛石或氧化鈹或碳化矽材料。

一第一微波傳輸線陣列2,該第一微波傳輸線陣列2蒸鍍在第一載體基片1的上表面,該第一微波傳輸線陣列2的每個傳輸線單元採用的是共面波導或微帶傳輸線;該第一微波傳輸線陣列2用來給光子集成晶片提供偏置電壓和高頻調製信號;在此實施例中,該第一微波傳輸線陣列2用來給光子集成晶片中的直接調製雷射器陣列提供直流偏置電壓和高頻調製信號,如圖7,第一微波傳輸線陣列2採用共面波導結構,有12個傳輸線單元。

一第二載體基片3;其中該第二載體基片可採用氮化鋁或氮化鈹或氧化鋁或金剛石或氧化鈹或碳化矽材料。

一第二微波傳輸線陣列4,該第二微波傳輸線陣列4蒸鍍在第二載體基片3的下表面,該第二微波傳輸線陣列4的每個傳輸線單元採用的是共面波導或微帶傳輸線;與第一微波傳輸線陣列2的電極相匹配並進行焊接或燒結;使得第一微波傳輸線陣列2的每個信號電極單元與第二微波傳輸線陣列4的與之對應的信號電極單元接觸良好,相應的地電極也接觸良好,如圖6、圖7中的2-1與4-1,2-2與4-2。

一電極陣列5,該電極陣列5蒸鍍在第二載體基片3的一個側面或者相對的兩個側面;其邊緣幾何尺寸與第二微波傳輸線陣列4中的信號電極陣列相連線並過渡,如圖6中的5-1與4-1,5-2與4-2,在該實施例二中,電極陣列5蒸鍍在第二載體基片3的兩個側面,共有12個信號電極單元。

一L型電極陣列10,該L型電極陣列10蒸鍍在第二載體基片3的兩個側面及上表面,如圖6中的5-1與10-1,5-2與10-2,共有12個電極單元,與電極陣列5的每個信號電極單元一一對應。

一電感陣列11,該電感陣列11安裝在第二載體基片3的兩個側面,共有12個電感單元,與電極陣列5的每個信號電極單元一一對應。如圖6中的5-1與11-1,5-2與11-2,將電感陣列11的一端與信號電極陣列5對應焊接,用互連金絲組12將電感陣列11的另外一端與L型電極陣列10對應連線,作為光子集成晶片直流偏置網路的一部分。

一直接調製雷射器晶片陣列13,在該實施例二中,該直接調製雷射器晶片陣列13包含12個雷射器,通過互連金絲組14與第一微波傳輸線陣列2的傳輸線單元對應連線。該直接調製雷射器晶片陣列13與第一微波傳輸線陣列2、第二微波傳輸線陣列4、電極陣列5、電感陣列11、L型電極陣列10、互連金絲組12、互連金絲組14一同構成了該光子集成晶片中的直流偏置網路。

一薄膜電阻陣列15,該薄膜電阻陣列15蒸鍍在第一載體基片1的上表面,其材料為氮化鉭或鎳鉻合金。該薄膜電阻陣列15與第一微波傳輸線陣列2對應連線,接觸良好。該薄膜電阻陣列15中的每個電阻單元的阻值,根據第一微波傳輸線陣列2的共面波導結構或者微帶結構的特徵阻抗值以及直接調製雷射器晶片陣列13的交流阻抗值共同確定。該薄膜電阻陣列15與第一微波傳輸線陣列2、直接調製雷射器晶片陣列13、互連金絲組14共同構成該光子集成晶片中的交流通路。

專利榮譽

2021年6月24日,《光子集成晶片匹配電路的三維封裝裝置》獲得第二十二屆中國專利優秀獎。