專利背景

2015年前,針對兩個以上電容串聯作為母線支撐電容拓撲結構中,電容的狀態監測是一個非常重要的環節。針對2015年前公布的資料,只蒐集到一篇相關專利,即申請號為201180060158.2的中國發明專利公開了一種電容器的異常檢測方法及異常檢測裝置。該發明提供用於在串聯連線兩個以上的電容器的電路中準確地檢測個別電容器的異常的檢測方法及檢測裝置。該發明的電容異常檢測裝置包括:從上述電路的兩端測量上述電路的電容的測量部;存儲所測量的上述電路的電容及測量時的電路使用時間的存儲部;以及對所測量的上述電路與已經設定的預測電容進行比較,判斷構成上述電路的至少一個電容器是否發生異常的判斷部。

因此,2015年之前技術的電容異常檢測方法需要測量電容的容值,方法較為複雜,在現場套用時有其局限性。

發明內容

專利目的

《一種電容異常檢測系統及其工作方法》的目的是提供一種電容異常檢測系統及其工作方法,有效檢測兩個以上電容串聯狀態中電容異常檢測,滿足高壓大功率電力電子系統的可靠性要求。

技術方案

《一種電容異常檢測系統及其工作方法》提供了一種電容異常檢測系統,其特徵在於,所述電容異常檢測系統適用於兩個以上電容串聯作為母線支撐電容的拓撲電路;所述電容異常檢測系統包括:直流母線採集單元,用於採集母線兩端電壓;電容電壓採集單元,用於採集位於拓撲電路中首、尾電容之間的相應電容的一端電壓值;所述直流母線採集單元、電容電壓採集單元分別與一運算單元相連,該運算單元適於根據對直流母線採集單元、電容電壓採集單元獲得的相應電壓值計算出適於判斷任一母線支撐電容出現異常時的判斷電壓值。

進一步,若所述電容的個數為三個,則所述運算單元包括:第一、第二減法器,其中第一、第二減法器的反相輸入端分別與直流母線採集單元的兩輸出端相連;第一、第二減法器的同相輸入端分別與電容電壓採集單元的輸出端相連;所述第一、第二減法器的輸出端分別與混合運算電路的兩輸入端相連,該混合運算電路將第一、第二減法器的計算結果進行反相求和後,再與一基準電壓進行比較以獲得所述判斷電壓值。

進一步,所述混合運算電路包括:反相加法電路、與該反相加法電路相連的比較器;所述反相加法運算電路包括集成運算放大器U2C、該集成運算放大器U2C的反相輸入端通過電阻R12、電阻R14分別與第一、第二減法器的輸出端相連;所述集成運算放大器U2C的輸出端與比較器的一輸入端相連,該比較器的另一輸入端接入所述基準電壓,所述比較器適於輸出判斷電壓值。

進一步,所述直流母線採集單元的兩輸出端、電容電壓採集單元的輸出端分別與第一、第二、第三跟隨器相連,且通過各跟隨器連線第一、第二減法器的反相輸入端、同相端;以及所述集成運算放大器U2C的輸出端與比較器之間設有第四跟隨器。

進一步,所述運算單元適於將判斷電壓值傳送至處理器模組,所述處理器模組還與顯示模組、按鍵相連;以及所述處理器模組的控制端連線所述基準電壓的供電模組,以適於調節所述供電模組的輸出電壓。

進一步,若所述電容的個數大於三個,則所述運算單元還包括多選一模擬開關,所述多選一模擬開關的多路輸入端分別與首、尾電容之間的各電容的各端相連,且輸出端連線第二跟隨器的輸入端相連;所述多選一模擬開關的控制端由所述處理器模組控制。

又一方面,《一種電容異常檢測系統及其工作方法》還提供了一種電容異常檢測系統的工作方法,所述電容異常檢測系統適用於兩個以上電容串聯作為母線支撐電容的拓撲電路;包括如下步驟:

步驟S1,採集母線兩端電壓;

步驟S2,採集位於拓撲電路中首、尾電容之間的相應電容的一端電壓值;

步驟S3,根據對直流母線採集單元、電容電壓採集單元獲得的相應電壓值計算出適於判斷任一母線支撐電容出現異常時的判斷電壓值。

進一步,通過直流母線採集單元採集母線兩端電壓;通過電容電壓採集單元母線兩端電壓的直流母線採集單元;以及所述直流母線採集單元、電容電壓採集單元分別與一運算單元相連,該運算單元適於計算所述判斷電壓值。

進一步,若所述電容的個數為三個,則所述運算單元包括:第一、第二減法器,其中第一、第二減法器的反相輸入端分別與直流母線採集單元的兩輸出端相連;第一、第二減法器的同相輸入端分別與電容電壓採集單元的輸出端相連;所述第一、第二減法器的輸出端分別與混合運算電路的兩輸入端相連,該混合運算電路將第一、第二減法器的計算結果進行反相求和後,再與一基準電壓進行比較以獲得所述判斷電壓值;所述混合運算電路包括:反相加法電路、與該反相加法電路相連的比較器;所述反相加法運算電路包括集成運算放大器U2C、該集成運算放大器U2C的反相輸入端通過電阻R12、電阻R14分別與第一、第二減法器的輸出端相連;所述集成運算放大器U2C的輸出端與比較器的一輸入端相連,該比較器的另一輸入端接入所述基準電壓,所述比較器適於輸出判斷電壓值;所述運算單元適於將判斷電壓值傳送至處理器模組,所述處理器模組還與顯示模組、按鍵相連;以及所述處理器模組的控制端連線所述基準電壓的供電模組,以適於調節所述供電模組的輸出電壓。

進一步,若所述電容的個數大於三個,則所述運算單元還包括多選一模擬開關,所述多選一模擬開關的多路輸入端分別與首、尾電容之間的各電容的各端相連,且輸出端連線第二跟隨器的輸入端相連;所述多選一模擬開關的控制端由所述處理器模組控制。

有益效果

《一種電容異常檢測系統及其工作方法》的有益效果是,該發明的電容異常檢測系統及其工作方法,有效檢測兩個以上電容串聯狀態中電容異常檢測,提高了高壓大功率電力電子系統的可靠性;並且該發明還使對電容異常報警信號的判斷至限於母線支撐電容是否出現不均壓有關,而與輸入直流母線電壓的大小無關;通過調節兩個減法器的反饋電阻和比較器的參考電壓,使母線支撐電容在發生異常時,均壓誤差控制在一定的範圍內不會報警,超出此範圍就會發生報警,提高了整個檢測系統的容錯能力。

附圖說明

圖1是《一種電容異常檢測系統及其工作方法》的三個母線支撐電容拓撲電路的電路圖;

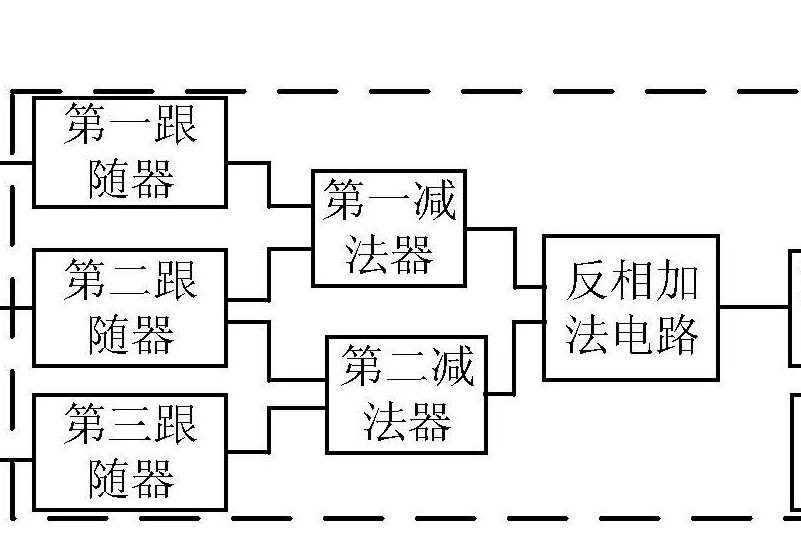

圖2是《一種電容異常檢測系統及其工作方法》的三個母線支撐電容的拓撲電路所涉及的電容異常檢測系統的原理框圖;

圖3是《一種電容異常檢測系統及其工作方法》的三個母線支撐電容的拓撲電路所涉及的電容異常檢測系統原理圖;

圖4是《一種電容異常檢測系統及其工作方法》的四個母線支撐電容拓撲電路的電路圖;

圖5是《一種電容異常檢測系統及其工作方法》的四個母線支撐電容的拓撲電路所涉及的電容異常檢測系統的原理框圖。

技術領域

《一種電容異常檢測系統及其工作方法》涉及一種電容異常檢測方法及檢測系統。

權利要求

1.一種電容異常檢測系統,其特徵在於,所述電容異常檢測系統適用於兩個以上電容串聯作為母線支撐電容的拓撲電路;所述電容異常檢測系統包括:直流母線採集單元,用於採集母線兩端電壓;電容電壓採集單元,用於採集位於拓撲電路中首、尾電容之間的相應電容的一端電壓值;所述直流母線採集單元、電容電壓採集單元分別與一運算單元相連,該運算單元適於根據對直流母線採集單元、電容電壓採集單元獲得的相應電壓值計算出適於判斷任一母線支撐電容出現異常時的判斷電壓值。

2.根據權利要求1所述的電容異常檢測系統,其特徵在於,若所述電容的個數為三個,則所述運算單元包括:第一、第二減法器,其中第一、第二減法器的反相輸入端分別與直流母線採集單元的兩輸出端相連;第一、第二減法器的同相輸入端分別與電容電壓採集單元的輸出端相連;所述第一、第二減法器的輸出端分別與混合運算電路的兩輸入端相連,該混合運算電路將第一、第二減法器的計算結果進行反相求和後,再與一基準電壓進行比較以獲得所述判斷電壓值。

3.根據權利要求2所述的電容異常檢測系統,其特徵在於,所述混合運算電路包括:反相加法電路、與該反相加法電路相連的比較器;所述反相加法運算電路包括集成運算放大器U2C、該集成運算放大器U2C的反相輸入端通過電阻R12、電阻R14分別與第一、第二減法器的輸出端相連;所述集成運算放大器U2C的輸出端與比較器的一輸入端相連,該比較器的另一輸入端接入所述基準電壓,所述比較器適於輸出判斷電壓值。

4.根據權利要求3所述的電容異常檢測系統,其特徵在於,所述直流母線採集單元的兩輸出端、電容電壓採集單元的輸出端分別與第一、第二、第三跟隨器相連,且通過各跟隨器連線第一、第二減法器的反相輸入端、同相端;以及所述集成運算放大器U2C的輸出端與比較器之間設有第四跟隨器。

5.根據權利要求4所述的電容異常檢測系統,其特徵在於,所述運算單元適於將判斷電壓值傳送至處理器模組,所述處理器模組還與顯示模組、按鍵相連;以及所述處理器模組的控制端連線所述基準電壓的供電模組,以適於調節所述供電模組的輸出電壓。

6.根據權利要求5所述的電容異常檢測系統,其特徵在於,若所述電容的個數大於三個,則所述運算單元還包括多選一模擬開關,所述多選一模擬開關的多路輸入端分別與首、尾電容之間的各電容的各端相連,且輸出端連線第二跟隨器的輸入端相連;所述多選一模擬開關的控制端由所述處理器模組控制。

7.一種電容異常檢測系統的工作方法,所述電容異常檢測系統適用於兩個以上電容串聯作為母線支撐電容的拓撲電路;其特徵在於,包括如下步驟:

步驟S1,採集母線兩端電壓;

步驟S2,採集位於拓撲電路中首、尾電容之間的相應電容的一端電壓值;

步驟S3,根據對直流母線採集單元、電容電壓採集單元獲得的相應電壓值計算出適於判斷任一母線支撐電容出現異常時的判斷電壓值。

8.根據權利要求7所述的工作方法,其特徵在於,通過直流母線採集單元採集母線兩端電壓;通過電容電壓採集單元母線兩端電壓的直流母線採集單元;以及所述直流母線採集單元、電容電壓採集單元分別與一運算單元相連,該運算單元適於計算所述判斷電壓值。

9.根據權利要求8所述的工作方法,其特徵在於,若所述電容的個數為三個,則所述運算單元包括:第一、第二減法器,其中第一、第二減法器的反相輸入端分別與直流母線採集單元的兩輸出端相連;第一、第二減法器的同相輸入端分別與電容電壓採集單元的輸出端相連;所述第一、第二減法器的輸出端分別與混合運算電路的兩輸入端相連,該混合運算電路將第一、第二減法器的計算結果進行反相求和後,再與一基準電壓進行比較以獲得所述判斷電壓值;所述混合運算電路包括:反相加法電路、與該反相加法電路相連的比較器;所述反相加法運算電路包括集成運算放大器U2C、該集成運算放大器U2C的反相輸入端通過電阻R12、電阻R14分別與第一、第二減法器的輸出端相連;所述集成運算放大器U2C的輸出端與比較器的一輸入端相連,該比較器的另一輸入端接入所述基準電壓,所述比較器適於輸出判斷電壓值;所述運算單元適於將判斷電壓值傳送至處理器模組,所述處理器模組還與顯示模組、按鍵相連;以及所述處理器模組的控制端連線所述基準電壓的供電模組,以適於調節所述供電模組的輸出電壓。

10.根據權利要求9所述的工作方法,其特徵在於,若所述電容的個數大於三個,則所述運算單元還包括多選一模擬開關,所述多選一模擬開關的多路輸入端分別與首、尾電容之間的各電容的各端相連,且輸出端連線第二跟隨器的輸入端相連;所述多選一模擬開關的控制端由所述處理器模組控制。

實施方式

《一種電容異常檢測系統及其工作方法》的電容異常檢測系統及其工作方法均適用於兩個以上電容串聯作為母線支撐電容的拓撲電路。

其中,所述拓撲電路的電路結構如圖1所示,圖中,電阻R1’、電阻R2’串聯後分別與電容C1’相併聯,同樣,電阻R3’、電阻R4’串聯後分別與電容C2’、電阻R5’、電阻R6’串聯後分別與電容C3’構成拓撲電路,其中,電容C1’、電容C2’、電容C3’為母線支撐電容。

D端(直流母線正端)和G端(直流母線負端)分別為母線兩端,C端為首、尾電容之間的電容C2’的一端,所述電容C2’的一端還連線有分壓電路,以對電容電壓採集單元的採集電壓進行降壓,所述分壓電路例如由電阻R100、電阻R200、電阻R300和電容C100、電容C200組成,具體的,從電阻R4’的兩端引出,即電阻R4’的第一端與由電阻R300和電容C100構成的並聯電路相連後接地,並且電阻R4’的第二端通過電阻R100與由電阻R200和電容C200構成的並聯電路相連後接地。

通過圖1可以推導出3個母線支撐電容、4個母線支撐電容構成的拓撲電路。

實施例1

如圖1和圖2所示,《一種電容異常檢測系統及其工作方法》的一種電容異常檢測系統,所述電容異常檢測系統適用於兩個以上電容串聯作為母線支撐電容的拓撲電路;所述電容異常檢測系統包括:直流母線採集單元,用於採集母線兩端電壓;電容電壓採集單元,用於採集位於拓撲電路中首、尾電容之間的相應電容的一端電壓值;所述直流母線採集單元、電容電壓採集單元分別與一運算單元相連,該運算單元適於根據對直流母線採集單元、電容電壓採集單元獲得的相應電壓值計算出適於判斷任一母線支撐電容出現異常時的判斷電壓值。

其中,在圖1中,首、尾電容分別為連線兩端母線的電容,例如圖1中的電容C1’、電容C3’。

進一步,若所述電容的個數為三個(電容C1’、電容C2’、電容C3’),則所述運算單元包括:第一、第二減法器,其中第一、第二減法器的反相輸入端分別與直流母線採集單元的兩輸出端相連;第一、第二減法器的同相輸入端分別與電容電壓採集單元的輸出端相連;所述第一、第二減法器的輸出端分別與混合運算電路的兩輸入端相連,該混合運算電路將第一、第二減法器的計算結果進行反相求和後,再與一基準電壓進行比較以獲得所述判斷電壓值。

所述混合運算電路包括:反相加法電路、與該反相加法電路相連的比較器;所述反相加法運算電路包括集成運算放大器U2C、該集成運算放大器U2C的反相輸入端通過電阻R12、電阻R14分別與第一、第二減法器的輸出端相連;所述集成運算放大器U2C的輸出端與比較器的一輸入端相連,該比較器的另一輸入端接入所述基準電壓,所述比較器適於輸出判斷電壓值。

所述直流母線採集單元的兩輸出端、電容電壓採集單元的輸出端分別與第一、第二、第三跟隨器相連,且通過各跟隨器連線第一、第二減法器的反相輸入端、同相端;以及所述集成運算放大器U2C的輸出端與比較器之間設有第四跟隨器。

所述運算單元適於將判斷電壓值傳送至處理器模組,所述處理器模組還與顯示模組、按鍵相連;以及所述處理器模組的控制端連線所述基準電壓的供電模組,以適於調節所述供電模組的輸出電壓。

針對三個母線支撐電容的拓撲電路所涉及的電容異常檢測系統的原理框圖的具體實施方式如圖3所示。

圖3中,電阻R1、電阻R2、電容C1、電阻R20、電阻R21、電容C11構成直流母線採集單元,D端與電阻R1一端相連,電阻R1另一端與電阻R2、電容C1相連,電阻R2另一端與地相連,電容C1的另一端與地相連,直流母線電壓經電阻R1、電阻R2相連處輸出;直流母線負端G處與電阻R21一端相連,電阻R21另一端與電阻R20、電容C11相連,電阻R20另一端與地相連,電容C11的另一端與地相連,直流母線電壓經電阻R21、電阻R20相連處輸出。

C端通過接線端子P1接入,電阻R6、電阻R7、電阻R8、電容C4、電容C5構成電容電壓採集單元。在圖3所示電路原理圖中,接線端子P1的1端與電阻R8、電容C4相連,電阻R8、電容C4的另一端與地相連,接線端子P1的2端(對應原理圖中標註為C處),與電阻R6相連,電阻R6的另一端與電阻R7、電容C5相連,電阻R7、電阻C5的另一端與地相連,電容電壓採集單元經電阻R6、電阻R7的相連處輸出。

第一、第二、第三跟隨器分別由集成運算放大器U1A、集成運算放大器U1B、集成運算放大器U1C、集成運算放大器U1D及外圍電路構成。

第一、第二減法器分別由集成運算放大器U2A、集成運算放大器U2B及外圍電路構成。

所述集成運算放大器U2C的輸出端還連線有穩壓管D1,且通過第四跟隨器接入比較器,該比較器由集成運算放大器U2D及外圍電路構成,具體的,第四跟隨器的輸出端連線集成運算放大器U2D的同相端,集成運算放大器U2D的反相端連線基準電壓,並且集成運算放大器U2D的輸出端經電阻R25、電容C15相連處輸出判斷電壓(CERROR)至處理器模組;通過觀測所述判斷電壓的電平狀態就可以判斷母線支撐電容是否發生異常。

如圖4和圖5所示,若所述電容的個數大於三個,則所述運算單元還包括多選一模擬開關,所述多選一模擬開關的多路輸入端分別與首、尾電容之間的各電容的各端相連,且輸出端連線第二跟隨器的輸入端相連;所述多選一模擬開關的控制端由所述處理器模組控制。

實施例2

如圖1至圖5所示,在實施例1基礎上,《一種電容異常檢測系統及其工作方法》還提供了一種電容異常檢測系統的工作方法,所述電容異常檢測系統適用於兩個以上電容串聯作為母線支撐電容的拓撲電路;所述工作方法包括如下步驟:

步驟S1,採集母線兩端電壓;

步驟S2,採集位於拓撲電路中首、尾電容之間的相應電容的一端電壓值;

步驟S3,根據對直流母線採集單元、電容電壓採集單元獲得的相應電壓值計算出適於判斷任一母線支撐電容出現異常時的判斷電壓值。

進一步,通過直流母線採集單元採集母線兩端電壓;通過電容電壓採集單元母線兩端電壓的直流母線採集單元;以及所述直流母線採集單元、電容電壓採集單元分別與一運算單元相連,該運算單元適於計算所述判斷電壓值。

進一步,若所述電容的個數為三個,則所述運算單元包括:第一、第二減法器,其中第一、第二減法器的反相輸入端分別與直流母線採集單元的兩輸出端相連;第一、第二減法器的同相輸入端分別與電容電壓採集單元的輸出端相連;所述第一、第二減法器的輸出端分別與混合運算電路的兩輸入端相連,該混合運算電路將第一、第二減法器的計算結果進行反相求和後,再與一基準電壓進行比較以獲得所述判斷電壓值。

所述混合運算電路包括:反相加法電路、與該反相加法電路相連的比較器;所述反相加法運算電路包括集成運算放大器U2C、該集成運算放大器U2C的反相輸入端通過電阻R12、電阻R14分別與第一、第二減法器的輸出端相連;所述集成運算放大器U2C的輸出端與比較器的一輸入端相連,該比較器的另一輸入端接入所述基準電壓,所述比較器適於輸出判斷電壓值;所述運算單元適於將判斷電壓值傳送至處理器模組,所述處理器模組還與顯示模組、按鍵相連;以及所述處理器模組的控制端連線所述基準電壓的供電模組,以適於調節所述供電模組的輸出電壓。

若所述電容的個數大於三個,則所述運算單元還包括多選一模擬開關,所述多選一模擬開關的多路輸入端分別與首、尾電容之間的各電容的各端相連,且輸出端連線第二跟隨器的輸入端相連;所述多選一模擬開關的控制端由所述處理器模組控制。

《一種電容異常檢測系統及其工作方法》將採樣後的C端電壓分別與D端、G端電壓比較,使電容異常報警信號只與母線支撐電容是否出現不均壓有關,而與輸入直流母線電壓的大小無關。通過調節兩個減法器的反饋電阻和比較器的參考電壓,可使母線支撐電容在發生異常時,均壓誤差範圍在1/5~2/5之間不會報警,超出此範圍就會發生報警。

榮譽表彰