專利背景

發光二極體(LED,LightEmittingDiode)是一種外延固體發光器件,通過在器件兩端載入正向電壓,電子和空穴在有源區複合產生大量光子,電能轉化為光能。而

氮化鎵基外延是繼Si和GaAs之後的第三代外延材料,近年來發展較為迅速。但同樣也面臨著很多問題,例如,當LED處於工作狀態時,大量的電子會從有源層溢出,使得發光效率大大降低。截至2015年12月,常採用的解決方法是在發光層之後生長一層P型氮化鋁鎵電子阻擋層,用以減少電子的溢出,同時還可以顯著降低外延片中P型層的位錯密度,減弱鎂的自補償效應以及減少甚至抑制非輻射複合中心的產生,提高空穴的注入效率。

截至2015年12月,大部分P型氮化鋁鎵是鋁組分是恆定不變的單層結構,隨著鎂的增加,氮化鋁鎵中空穴濃度單調上升,當空穴濃度達到最大後,隨著鎂的繼續增加,鎂的自補償效應,使空穴濃度反而下降,且材料劣化產生裂紋。因此,P型電子阻擋層結構的設計對氮化鎵基LED的內量子效率和發光效率有很重要的影響。

發明內容

專利目的

《一種具有電子阻擋與空穴調整層的外延結構》所解決的技術問題在於提供一種具有電子阻擋與空穴調整層的外延結構及製備方法,以解決上述背景技術中所提及的問題。

技術方案

《一種具有電子阻擋與空穴調整層的外延結構》提供的技術方案為:一種具有電子阻擋與空穴調整層的外延結構,從下至上依次包括襯底、緩衝層、N型摻雜半導體層、發光層和P型摻雜半導體層,其中,所述發光層與P型摻雜半導體層之間還包含材料為Alx0Iny0Ga1-x0-y0N的P型摻雜空穴注入層和複數個子組合層堆疊形成的多層結構;所述每一個子組合層由材料為Alx1Iny1Ga1-x1-y1N的電子阻擋層與材料為Alx2Iny2Ga1-x2-y2N的空穴調整層組成,其中,y0>x0>0,x1>y1>0,x2≥y2>0,x1>x2≥x0,y0>y2>y1。

優選的,所述多層結構中位於下部的子組合層為非故意P型摻雜層,位於上部的子組合層為故意P型摻雜層,所述非故意P型摻雜的子組合層個數大於或等於所述故意P型摻雜的子組合層個數。優選的,所述空穴注入層的P型雜質濃度大於多層結構的P型雜質濃度。優選的,所述空穴注入層形成過程中的P型雜質通過延遲效應及後續高溫條件下的擴散作用進入非故意P型摻雜子組合層內。優選的,所述故意P型摻雜的子組合層個數≤3。優選的,所述多層結構中至少2個子組合層的Al組分不同。優選的,所述多層結構中子組合層的個數≥2。優選的,每一所述子組合層的總厚度為10埃~200埃。優選的,所述空穴注入層的厚度為50埃~1000埃。

優選的,所述空穴注入層、電子阻擋層與空穴調整層的Al組分的變化方式為恆定摻雜、拋物線形、遞增或遞減變化摻雜。優選的,所述空穴注入層的P型雜質平均濃度≥1×10。優選的,所述多層結構的P型雜質平均濃度≥1×10。為製備上述的外延結構,該發明同時提出一種具有電子阻擋與空穴調整層的外延結構的製備方法,所述方法包括以下步驟:

提供一襯底;沉積緩衝層於所述襯底之上;沉積N型摻雜半導體層於所述緩衝層之上;沉積發光層於所述N型摻雜半導體層之上;沉積材料為Alx0Iny0Ga1-x0-y0N的P型摻雜空穴注入層於所述發光層之上;沉積材料為Alx1Iny1Ga1-x1-y1N的電子阻擋層與材料為Alx2Iny2Ga1-x2-y2N的空穴調整層交替堆疊組成的多層結構於所述空穴注入層之上,其中,y0>x0>0,x1>y1>0,x2≥y2>0,x1>x2≥x0,y0>y2>y1;沉積P型摻雜半導體層於所述多層結構之上,形成外延結構。

優選的,沉積所述P型摻雜空穴注入層時反應室的溫度低於沉積所述多層結構時反應室的溫度。

優選的,沉積所述P型摻雜空穴注入層時反應室的溫度與沉積所述多層結構時反應室的溫度差值為50~100℃。

優選的,沉積所述P型摻雜空穴注入層時反應室的壓力與沉積所述多層結構時反應室的壓力相同,壓力值為50~500托。

優選的,沉積多層結構過程中,首先停止通入P型雜質源,沉積位於多層結構下部的非故意P型摻雜子組合層,所述空穴注入層形成過程中的P型雜質通過延遲效應及後續高溫條件下的擴散作用進入所述非故意P型摻雜子組合層內;然後再次通入P型雜質源,沉積形成位於所述多層結構上部的故意P型摻雜子組合層。

優選的,所述非故意P型摻雜子組合層的個數大於或等於所述故意P型摻雜子組合層的個數。

優選的,所述故意P型摻雜子組合層的個數≤3。

優選的,所述空穴注入層的P型雜質濃度大於多層結構的P型雜質濃度。

優選的,所述空穴注入層的P型雜質平均濃度≥1×10。

優選的,所述多層結構的P型雜質平均濃度≥1×10。

優選的,所述多層結構中至少2個子組合層的Al組分不同。

優選的,所述多層結構中子組合層的個數≥2。

優選的,每一所述子組合層的總厚度為10埃~200埃。

優選的,所述空穴注入層的厚度為50埃~1000埃。

優選的,所述空穴注入層、電子阻擋層與空穴調整層的Al組分的變化方式為恆定摻雜、拋物線形、遞增或遞減變化摻雜。

《一種具有電子阻擋與空穴調整層的外延結構》通過在外延結構中的發光層與P型摻雜半導體層之間插入一層P型空穴注入層,以高濃度摻雜提供足夠的空穴,且臨近發光層,可有效提升發光效率,同時為緩衝發光層與後續多層結構的晶格差異及實現低能階特性,該空穴注入層採用低Al組分高In組分的材料組成。

隨後生長高Al組分的電子阻擋層和低Al組分的空穴調整層交替層疊組成的多層結構,利用高Al組分與低Al組分交替分布的結構避免高Al組分引起的材料質量降低現象,同時利用In組分低能階的特性與Al組分搭配調變多層結構的能階變化以進一步改善多層結構整體電子阻擋及空穴調整的作用。

此外,在沉積臨近空穴注入層的多層結構的子組合層時不通入P型雜質源,而是通過P型雜質的延遲效應及後續高溫條件下的擴散作用進入該子組合層內;然後在繼續生長的臨近P型摻雜半導體層的子組合層中摻入P型雜質,在保證不增加電壓特性的前提下,提升多層結構的晶體質量。

同時,所述空穴注入層和多層結構均為氮化鋁銦鎵材料層,調整多層結構中鋁和銦的組分含量,在形成良好的電子阻擋性能的同時降低其阻值,且結合前述的空穴注入層提供的有效空穴來源改善晶片的抗靜電性能。

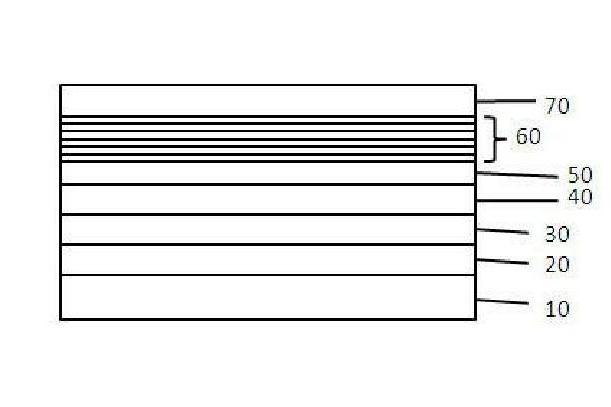

圖1為《一種具有電子阻擋與空穴調整層的外延結構》實施例一之發光半導體外延結構示意圖。

圖2為該發明實施例一之多層結構示意圖一。

圖3為該發明實施例一之多層結構示意圖二。

圖4為該發明實施例一之發光半導體外延結構的製備方法流程圖。

圖5為該發明實施例二之發光半導體外延結構示意圖。

圖6為該發明實施例二之多層結構示意圖。

圖中:10.襯底;20.緩衝層;30.N型摻雜半導體層;40.發光層;50.P型摻雜空穴注入層;60.多層結構;61、61’、62、62’.子組合層;611、611’、621、621’.電子阻擋層;612、612’、622、622’.空穴調整層;70.P型摻雜半導體層。

《一種具有電子阻擋與空穴調整層的外延結構》屬於半導體製備技術領域,特別涉及一種具有電子阻擋與空穴調整層的外延結構。

1.《一種具有電子阻擋與空穴調整層的外延結構》從下至上依次包括襯底、緩衝層、N型摻雜半導體層、發光層和P型摻雜半導體層,其特徵在於:所述發光層與P型摻雜半導體層之間還包含材料為Alx0Iny0Ga1-x0-y0N的P型摻雜空穴注入層和複數個子組合層堆疊形成的多層結構;所述每一個子組合層由材料為Alx1Iny1Ga1-x1-y1N的電子阻擋層與材料為Alx2Iny2Ga1-x2-y2N的空穴調整層組成,其中,y0>x0>0,x1>y1>0,x2≥y2>0,x1>x2≥x0,y0>y2>y1;所述多層結構中位於下部的子組合層為非故意P型摻雜層,位於上部的子組合層為故意P型摻雜層,所述非故意P型摻雜的子組合層個數大於或等於所述故意P型摻雜的子組合層個數。

2.根據權利要求1所述的一種具有電子阻擋與空穴調整層的外延結構,其特徵在於:所述空穴注入層形成過程中的P型雜質通過延遲效應及後續高溫條件下的擴散作用進入非故意P型摻雜子組合層內。

3.根據權利要求1所述的一種具有電子阻擋與空穴調整層的外延結構,其特徵在於:所述空穴注入層的P型雜質濃度大於多層結構的P型雜質濃度。

4.根據權利要求3所述的一種具有電子阻擋與空穴調整層的外延結構,其特徵在於:所述空穴注入層的P型雜質平均濃度≥1×10。

5.根據權利要求3所述的一種具有電子阻擋與空穴調整層的外延結構,其特徵在於:所述多層結構的P型雜質平均濃度≥1×10。

6.根據權利要求1所述的一種具有電子阻擋與空穴調整層的外延結構,其特徵在於:所述故意P型摻雜的子組合層個數≤3。

7.根據權利要求1所述的一種具有電子阻擋與空穴調整層的外延結構,其特徵在於:所述多層結構中至少2個子組合層的Al組分不同。

8.根據權利要求1所述的一種具有電子阻擋與空穴調整層的外延結構,其特徵在於:所述多層結構中子組合層的個數≥2。

9.根據權利要求1所述的一種具有電子阻擋與空穴調整層的外延結構,其特徵在於:每一所述子組合層的總厚度為10埃~200埃。

10.根據權利要求1所述的一種具有電子阻擋與空穴調整層的外延結構,其特徵在於:所述空穴注入層的厚度為50埃~1000埃。

11.根據權利要求1所述的一種具有電子阻擋與空穴調整層的外延結構,其特徵在於:所述空穴注入層、電子阻擋層與空穴調整層的Al組分的摻雜方式為恆定摻雜、拋物線形、遞增或遞減變化摻雜。

實施方式

參看附圖1和2,該發明提出的一種具有電流阻擋與空穴調整層的外延結構,包括襯底10、緩衝層20、N型摻雜半導體層30、發光層40、P型摻雜半導體層70;其中,發光層40與P型摻雜半導體層70之間還包含一材料為Alx0Iny0Ga1-x0-y0N、厚度為50埃~1000埃的P型摻雜空穴注入層50,以及複數個子組合層(61、61’62、和62’)堆疊形成的多層結構60;每一個子組合層均由材料為Alx1Iny1Ga1-x1-y1N的電子阻擋層(611、611’、621、621’)與材料為Alx2Iny2Ga1-x2-y2N的空穴調整層(612、612’、622、622’)組成,其中,y0>x0>0,x1>y1>0,x2≥y2>0,x1>x2≥x0,y0>y2>y1。由於P型摻雜空穴注入層50的主要作用是提供足夠的空穴濃度以增加電子空穴複合效率,因此為了使空穴較好的遷移進入發光層40,故設計該層的Al組分偏低,且為避免過高沉積溫度破壞發光層40質量,則採用較低沉積溫度,從而使該層的In摻雜組分偏高,即符合y0>x0>0的關係。而為了使多層結構60中的電子阻擋層(611、611’、621、621’)具有更好的電子阻擋效果,該層優選較高的Al組分,即x1>y1>0;同時為緩解較高Al組分所引起的材料質量降低現象,故隨後沉積的空穴調整層(612、612’、622、622’)採用較低Al組分,且為進一步最佳化Al與In的摻雜比例,得到更高的空穴調整作用,則該空穴調整層(612、612’、622、622’)的In組分與該層Al組分相近或略高,即x2≥y2>0。同時,為進一步提升P型摻雜空穴注入層50和多層結構60各自的功能作用,該發明進一步限定此兩層中Al組分和In組分的濃度,即x1>x2≥x0,y0>y2>y1。

多層結構60中至少2個子組合層(61、61’和62、62’)的Al組分不同;多層結構60中子組合層的個數≥2。每一子組合層的總厚度為10埃~200埃。其中,臨近於空穴注入層50的不同Al組分的子組合層61和62為非故意P型摻雜層,而臨近於P型摻雜半導體層70的不同Al組分的子組合層61’和62’為故意P型摻雜層,且子組合層61與61’,62與62’的Al組分相同,同時優選每一子組合層內電子阻擋層與空穴調整層內的Al組分相同,即層611和612、611’和612’、621和622、621’和622’的Al組分相同。

而作為此結構的一變形實施例,子組合層61與61’,62與62’為Al組分不同層,且按照61、62、61’、62’的順序為恆定摻雜或拋物線形或遞增或遞減變化,其x1和x2的變化範圍為:0.01~0.25,同時為了得到更好的效果,在調節鋁濃度變化時亦可調節銦的組分,使y1和y2的變化範圍為0.01~0.1。

參看附圖3,作為此結構的另一變形實施例,此多層結構60具有三個子組合層61、61’和62,其中,61、61’為未摻雜子組合層,62為P型摻雜子組合層;且Al組分不同,並按照61、61’、62、的順序亦可依照恆定摻雜或拋物線形或遞增或遞減變化,其x1和x2的變化範圍為:0.01~0.25。

參看附圖4,為製備上述外延結構,該發明同時提出一種製備方法,其包括以下步驟:

S01、提供一襯底10,襯底10選用藍寶石、碳化矽、矽、氮化鎵等材料中的一種;

S02、沉積緩衝層20於襯底10之上,緩衝層20為非摻雜氮化物層或低摻雜氮化物層;

S03、沉積N型摻雜半導體層30於緩衝層20之上;

S04、沉積發光層層40於N型半導體層30之上;

S05、調節反應室溫度至600~1000℃,壓力為50~500托,沉積材料為Alx0Iny0Ga1-x0-y0N的P型摻雜空穴注入層50於發光層40之上,其中,y0>x0>0,P型摻雜空穴注入層50的厚度為50埃~1000埃,其P型雜質濃度≥1×10,利用此高濃度P型摻雜提供充足的空穴,提高發光層40中的複合效率;且此高於後續多層結構60摻雜濃度的雜質亦為後續沉積層中雜質的遷移提供先決條件。同時該層沉積溫度略高於或等同於發光層40溫度,從而避免發光層40因高溫環境而被破壞;

S06、保持壓力不變,調節反應室溫度,使溫度高於空穴注入層50的沉積溫度50~100℃,沉積材料為Alx1Iny1Ga1-x1-y1N的電子阻擋層與材料為Alx2Iny2Ga1-x2-y2N的空穴調整層交替堆疊組成的多層結構60於空穴注入層50之上;與空穴注入層50的沉積溫度相比,該多層結構60的沉積溫度較高,利用此高溫條件提升晶體質量,減少缺陷,改善發光半導體的性能,其中y0>x0>0;x1>y1>0,x2≥y2>0,x1>x2≥x0,y0>y2>y1;S07、沉積P型摻雜半導體層70於多層結構60之上形成外延結構。

該發明中,所述多層結構60中至少包含2個Al組分不同的子組合層,每一個子組合層均由一對材料為Alx1Iny1Ga1-x1-y1N的電子阻擋層與材料為Alx2Iny2Ga1-x2-y2N的空穴調整層組成,且電子阻擋層和空穴調整層中Al組分的變化方式為恆定摻雜、拋物線形、遞增或遞減變化摻雜;該實施例中沉積多層結構60的具體過程為:在P型摻雜的空穴注入層50沉積結束後,停止通入P型雜質源,通過延遲效應及後續高溫條件下的擴散作用生長非故意P型摻雜的子組合層61,其由AAlx1Iny1Ga1-x1-y1N的電子阻擋層611與Alx2Iny2Ga1-x2-y2N的空穴調整層612組成,繼續沉積子組合層62,其亦由材料為Alx1Iny1Ga1-x1-y1N的電子阻擋層621與Alx2Iny2Ga1-x2-y2N的空穴調整層622組成,其中x1>y1>0,x2≥y2>0,此處優選x1=0.05~0.25,y1=0.01~0.1,x2=0.05~0.25,y2=0.01~0.1;所述組合層61和62為鋁組分不同的子組合層,優選子組合層61的Al組分高於子組合層62,且相比於空穴注入層50,其鋁和銦組分滿足關係式:x1>x2≥x0,y0>y2>y1。後通入P型雜質源,沉積鋁組分和銦組分分別與子組合層61和子組合層62相同或不同的子組合層61’和子組合層62’,其均由材料為Alx1Iny1Ga1-x1-y1N的電子阻擋層611’、621’及材料為Alx2Iny2Ga1-x2-y2N的空穴調整層612’、622’組成。

雖然臨近於空穴注入層50的子組合層61和62在生長過程中未通入雜質源,但其沉積溫度較高,而P型雜質源在高溫條件下亦有擴散作用,同時P型雜質源也具有記憶延遲效應,因此利用此兩種特性可使空穴注入層50中的高濃度P型雜質源及腔室中延遲遺留的P型雜質源進入臨近的非故意P型摻雜層內,在不影響晶體質量的前提下,也使得電阻較小,減小最終形成的半導體元件的使用電壓。而臨近於P型摻雜半導體層70的子組合層61’和62’因摻雜有P型雜質源,從而使得形成的多層結構中P型雜質濃度均值≥1×10,進一步降低半導體元件的使用電壓。

作為本方法的變形例,沉積的多層結構60具有2個或3個子組合層,臨近於空穴調整層的一個或2個子組合層為未摻雜層,而臨近於P型摻雜半導體層70的子組合層則為P型摻雜層。

同時,所述空穴注入層50和多層結構60均為氮化鋁銦鎵材料層,當鋁組分越高,其電子阻擋效果越好,但其應力也隨之增加造成晶體質量劣化,因此該實施例採用鋁組分變化的方法及多層堆疊的結構緩解該層應力,同時配合P型雜質源非摻雜/摻雜的模式調節該多層結構60的電阻值,進而獲得具有良好的電子阻擋性能及低阻值特性的P型結構層,同時再利用高濃度空穴注入層50提供有效空穴注入來源,改善晶片的抗靜電性能。

參看附圖5和6,該實施例與實施例1的區別在於多層結構60中臨近空穴注入層50的非故意P型摻雜的子組合層(61、62、…)數目大於3,隨後在此非故意P型摻雜的子組合層上繼續沉積故意P型摻雜子組合層(61’、62’…),後將此非故意P型摻雜的子組合層與P型摻雜子組合層依次堆疊最終形成多層結構60。其中臨近空穴注入層50的非故意P型摻雜的子組合層及其上沉積的故意P型摻雜子組合層數目根據實際生產的電性能需求靈活調節,不局限於該實施例的數目。而為最佳化多層結構60對於電流阻擋效果及抗靜電性能,當多層結構60中子組合層數目大於8時,優選摻雜的子組合層數目小於等於3。

榮譽表彰

2020年7月17日,《一種具有電子阻擋與空穴調整層的外延結構》獲得安徽省第七屆專利獎銀獎。